Intel fue la primera en el ámbito de los PCs en incorporar SMT en sus procesadores, con la tecnología Hyper Threading de sus Pentium 4. Algo que se ha mantenido hasta ahora, pero no en todos, como vemos en el caso de los E-cores. Sin embargo, ahora Intel tomará una decisión aún más radical al respecto, eliminar HT por completo en sus Intel Lunar Lake. ¿Por qué?

Te interesará conocer más sobre qué es SMT

Intel Hyper Threading: la tecnología que dice adiós tras 22 años

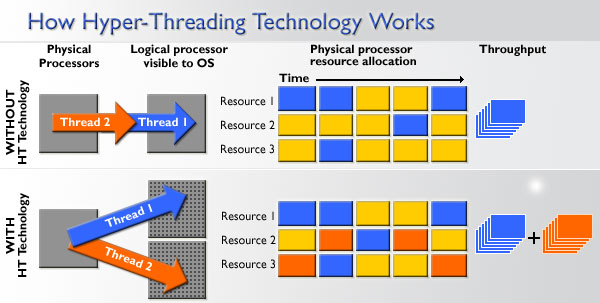

La tecnología Intel Hyper-Threading, o HTT, lleva más de dos décadas en el mercado. Fue introducida por Intel a principios de la década del 2000, con el objetivo de mejorar el rendimiento de los procesadores al permitir que cada núcleo físico simule dos núcleos lógicos.

La tecnología es totalmente transparente desde el lado del software, ya que el sistema operativo y los programas no tienen que tener constancia de ello. Para que funcione, tan solo se necesita un sistema operativo que soporte SMP (Symmetric MultiProcessing), y así funcionará. De esta forma, el sistema operativo no diferenciará entre los núcleos físicos y los lógicos, «creyendo» que tiene más núcleos disponibles para distribuir las tareas o hilos.

Por ejemplo, si tenemos un dual-core con HT de 2-way, esto significará que cada núcleo físico puede desdoblarse en dos núcleos lógicos, por lo que el planificador del sistema operativo cree que tiene 4 núcleos en total. Para mejorar el rendimiento, los schedulers o planificadores del sistema operativo se modifican para evitar que, por ejemplo, si se van a ejecutar solo dos threads se asignen solo a un núcleo físico, haciendo que ese núcleo esté muy ocupado mientras los otros permanecen inactivos. Eso sí, como sabrás, los hilos que pertenecen a un mismo proceso comparten algunos recursos, mientras que los procesos diferentes no comparten recursos entre sí, sino que tienen diferentes espacios de memoria, etc.

Cuando se ejecuta un proceso o programa, si ha sido programado para ello, se dividirá en distintos threads o partes más pequeñas que deben ejecutarse para completar el proceso. Básicamente será como si para el sistema no existe un solo núcleo, sino dos, pudiendo aprovechar mejor las unidades funcionales del núcleo haciendo que estén más ocupadas, cambiando de contexto y compartiendo tiempo entre dos threads o hilos de un mismo proceso. De esta forma, según la propia Intel, se conseguían mejoras de rendimiento de entorno al 15-30% (con solo un 5% de área extra ocupada en la superficie de silicio), ya que si un hilo no tiene disponibles los operandos para sus instrucciones, puede pasar a procesarse otro que sí las tiene, y así evitando que haya tiempos con unidades desocupadas durante más ciclos.

El concepto multithreading viene de la década de los años 50s, mientras que los primeros experimentos SMT (simultaneous multithreading) datan de 1968, en el proyecto IBM ACS-360.

SMT no era nada nuevo cuando lo introdujo Intel en sus Pentium 4 HT «Northwood» allá por el 2002. La tecnología que se esconde detrás de la marca registrada de Hyper Threading de Intel fue descrita por primera vez en 1973, por Edward S. Davidson y Leonard E. Shar.

En 1982, la compañía Denelcor Inc., crearon el primer producto que utilizaba esta tecnología, y fue llamado HEP (Heterogeneous Element Processor), que podía introducir varias instrucciones pertenecientes al mismo proceso al mismo tiempo en la pipeline. Si una instrucción bloqueaba la pipeline esperando los valores sobre los que debía operar, entonces se vaciaba la pipeline y se introducía otra instrucción que estuviera lista.

Otras compañías también experimentaron con este paradigma denominado SMT. De hecho, la tecnología tal como la conocemos actualmente fue patentada por primera vez por Kenneth Okin, que trabajaba para Sun Microsystems. Sería en 1994, para implementarlo en los SPARC. En ese momento, los procesos de fabricación de chips estaban suficientemente maduros para implementar SMT de forma rentable.

DEC Alpha 21464 (EV8) «Araña» fue otro de las primeras implementaciones de un microprocesador SMT 4-way más tempranas. Sin embargo, Didigtal Equipment Corp. había sido adquirida por Compaq y ésta a su vez por HP, abandonando el proyecto. La CPU no fuer comercializada finalmente, el proyecto se canceló en 2001. Dean Tullsen, Susan Eggers y Henry Levy fueron tres de los arquitectos principales de este procesador. Dean Tullsen terminaría trabajando en el desarrollo de Hyper Threading tras recalar en Intel. Muchos de los ingenieros «pata negra» de DEC fueron algunos de los artífices de los procesadores más exitosos de AMD e Intel, Jim Keller es un ejemplo, padre de AMD Zen, y de AMD64.

La primera vez que aterrizó en un x86 fue en 2002, para el Intel Xeon «Foster MP» y en el Intel Pentium 4 «Northwood» a 3.06 Ghz y «Prescott», vendiendo los procesadores bajo la marca Pentium 4 HT. Después llegarían otros como el Pentium 4 Extreme Edition. Sin embargo, la microarquitectura Core dejó de usar Hyper Threading, pueso que no era una evolución de los anteriores, sino que descendía directamente de la microarquitectura P6, la misma en la que se basaron los Pentium Pro, Pentium II y Pentium III, así como sus variantes Celeron y Xeon.

Con el Intel Core i7 «Nehalem», en 2008, la tecnología Hyper Threading aparecería de nuevo, e iría alternando procesadores con y sin HT hasta nuestros días. Ahora parece que con Lunar Lake podría desaparecer definitivamente, casi un cuarto de siglo más tarde. También se incluiría en los IA-64 de Intel, es decir, en los Itanium, siendo el primero en tenerla el Itanium 9300 «Montecito». El Itanium 9500 «Poulson» incluyó una arquitectura 8-way, es decir, con 8 núcleos virtuales o lógicos por núcleo.

Los términos SMT2, SMT4, SMT8, etc., o 2-way, 4-way, 8-way, etc., son equivalentes. Describen lo mismo, la cantidad de threads por núcleo.

Las unidades Intel Xeon Phi, usadas como aceleradores por hardware para HPC, basados en x86, también usaron un concepto similar a SMT, pero con lo que se conoce como Time-multiplexed multithreading 4-way. Es decir, un concepto temporal, que alterna entre hilos.

Hay que decir también que otros competidores de Intel también usaron SMT para sus procesadores, como el caso de los POWER 5 de IBM de 2005, con diseños 2-way, 4-way para el POWER 7 y 8-way para el POWER 8, lo que significa 2, 4 y 8 núcleos lógicos o threads por cada núcleo físico respectivamente. El IBM z13 también utilizaría un diseño 2-way. Otros como MIPS también usarían SMT, denominado MIPS MT en las microarquitecturas implementadas por la compañía RMI.

Hubo una arquitectura llamada VISC que usaba Virtual Software Layer para despachar un solo thread de instrucciones al Global Front-End, y que luego divide las instrucciones en lo que se conoce como threadlets de hardware virtual, para despacharlos a núcleos virtuales separados. Estos núcleos virtuales pueden usar recursos de hardware de cualquiera de los núcleos físicos.

Así como AMD también terminaría por abrazar SMT, aunque incialmente se opuso a estos diseños, e incluso se llegó a hablar de Anti-HT. De hecho, en AMD Bulldozer (Fusion), la microarquitectura usó un concepto FlexFPU que permitía el multithreading, mientras que el cauce para enteros solo permitía ejecutar un solo hilo. Es decir, eran solo parcialmente SMT. No sería hasta la llegada de Zen cuando comenzó a usar SMT 2-way convencional en sus Ryzen.

El concepto de AMD se basó en las técnicas CMP (Chip MultiProcessing), mismo concepto con el que experimentó Sun Microsystems (adquirida por Oracle) tras el UltraSPARC T1 «Niagara» de 2005 (este procesador no usaba SMT puro, sino que en cada ciclo alternaba entre un thread y otro), cuando canceló un proyecto que trataba de explotar lo mejor de CMP y SMT (lo denominó CMT) y cuyo nombre clave fue Rock, pero que sería cancelado en 2010.

CMP integra varios núcleos, cada uno con su propia unidad de control, caché y otras unidades funcionales comunes con el objetivo de aumentar la paralización, pero en el caso de AMD compartiendo un recurso como la FPU.

Ya como parte de Oracle, el SPARC T3 seguiría con la línea de multihilo temporal, alternando entre ciclos, esta vez 8-way de grano fino, seguido de los diseños SPARC T4, SPARC T5, SPARC M5, M6, y M7, estos últimos también 8-way, pero 2 de los threads podían ser ejecutados en paralelo, sin necesidad de alternar en cada ciclo. Es decir, eran parcialmente SMT y multihilo temporal.

Otros optaron por implementaciones diferentes, como Fujitsu para su SPARC64 VI, que usaría lo que se conoce como VMT o Vertical MultiThreading, volviendo nuevamente al SMT convencional de 2-way para el SPARC64 VII.

VMT se refiere a un SMT que puede procesar varios hilos compartiendo unidad de ejecución común, pero en diferentes etapas de la pipeline de instrucciones. Es decir, los hilos se ejecutan en la misma unidad de ejecución, pero de forma secuencial en momentos diferentes.

Por otro lado, Arm fue otra de las que se opuso totalmente al SMT. Y no solo Arm, también otros diseños que usan ISA ARM, como los Apple Silicon. ¿Por qué? Bueno, cuando se lanzaron los primeros HT, ni Windows ni Linux, ni otros sistemas operativos estaban optimizados para ello. Fue duramente criticado por ello, y la empresa Arm declaró que el SMT puede empeorar la eficiencia energética de un procesador de forma significativa, incluso dijo que estimaba que consumía un 46% más que si se usaban dos núcleos físicos. También analizaron el uso de la caché, que se incrementaba en un 42% más debido al thrashing.

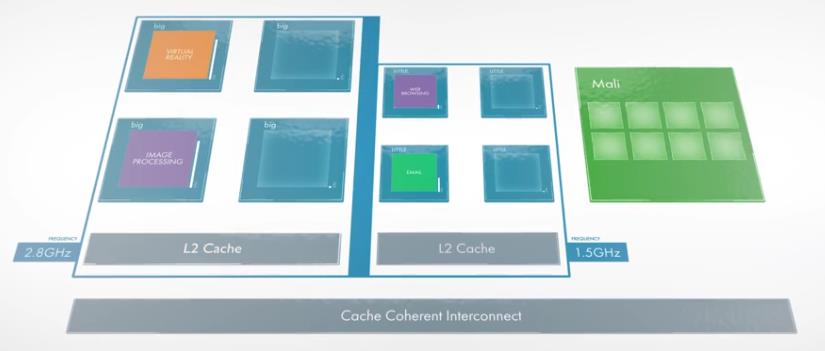

En 2010, Arm parecía que cambiaría de opinión, asegurando que podría incluir SMT en sus futuros diseños, pero eso no fue así, ya que prefirieron pasar a 64-bit, o ARM64, antes que usar SMT para seguir manteniendo su eficiencia. Intel seguiría finalmente los pasos de Arm, no solo adoptando el multinúcleo heterogéneo, con núcleos P-Core y E-Core, también abandonando el SMT para sus núcleos E-Core.

En cuanto a la seguridad de SMT, ya sabemos que puede tener serios problemas si no se implementa correctamente. En 2017 se detectaron graves problemas en los Skylake y Kaby Lake de Intel, y que podían causar la pérdida de datos, por lo que se necesitaron actualizaciones del microcódigo.

Coffe Lake también se alejaría de Hyper Threading, solo se incluiría en los Core i9 y Pentium Gold. Incluso, desde la compañía recomendaron deshabilitar HT desde el BIOS/UEFI para mitigar los ataques por las vulnerabilidades detectadas. Muchos investigadores habían empezado a investigar estos diseños, desvelando varios side-channel attacks, o ataques de canal lateral que podían usarse para obtener datos de la caché, como podían ser contraseñas, etc. Algo que se valía de hilos maliciosos para ello. Conoverás seguro vulnerabilidades como Foreshadow/L1TF, entre otras.

Otras críticas apuntaban a la pérdida de rendimiento cuando alguno de los recursos compartidos por hilos causaba cuellos de botella. La SMT comenzaba a flaquear desde todos los aspectos, y se obligó a los desarrolladores a implementar medias en los sistemas operativos actuales en sus APIs para evitar que procesos puedan coger recursos compartidos entre sí, dando lugar a problemas de seguridad. El castillo de naipes se comenzaba a derrumbar…

Lunar Lake y la desaparición de Hyper Threading

Intel ha eliminado Hyper-Threading en sus nuevos procesadores Lunar Lake. Algo que parecía ya casi cantado debido a los problemas citados anteriormente. Esta decisión, que sorprendió a muchos, se debe a la búsqueda de una mayor eficiencia energética en dispositivos portátiles. Al eliminar Hyper-Threading, Intel logra un mejor rendimiento por vatio en los núcleos de sus procesadores, sin sacrificar significativamente el rendimiento en tareas de un solo hilo.

Intel se ha dado cuenta de que puede implementar mayor cantidad de núcleos E-Core y eliminar núcleos lógicos problemáticos para mantener una cantidad de hilos considerable, pero todos ellos en núcleos físicos.

¿Por qué es importante? Bueno, pues esta decisión trae consigo las siguientes mejoras:

- Mayor eficiencia energética: al eliminar la necesidad de componentes adicionales para Hyper-Threading, los procesadores Lunar Lake consumen menos energía, lo que se traduce en una mayor duración de la batería en portátiles.

- Se elimina complejidad: al eliminar la tecnología, se puede reducir la cantidad de silicio empleado, lo cual puede ser otra ventaja.

- Enfoque en el rendimiento single-thread: se pueden centrar más en mejorar el rendimiento de un solo hilo, optimizando así el desempeño sin necesidad de agregar complejidad al planificador, etc.

En definitiva, lo que tenemos es un menor rendimiento multihilo, sí, esto es cierto, por lo que los Lunar Lake podrían tener capacidad para menos hilos que los actuales e incluso perder rendimiento contra AMD en tareas donde el SMT es importante, como el renderizado 3D, edición de vídeo, etc., pero siguen los pasos de Arm que parece que están funcionando bastante bien, sin tantos problemas.

Te recomiendo leer nuestra guía con los mejores procesadores del mercado

¿Esto significa que SMT desaparece del todo? ¿O al menos Hyper Threading se despide definitivamente? Lo cierto es que no, ya que Intel continuará usando Hyper Threading para otras microarquitecturas para el escritorio, servidores y HPC, donde la eficiencia energética no es prioritaria. Así que, no es un adiós, sino un hasta luego…

Y, tal vez, cuando madure la tecnología, y se pueda mejorar la eficiencia del Hyper Threading y limitar los problemas de seguridad, tal vez volverá en futuros diseños para portátiles.

Deja tus comentarios, serán bienvenidos…