AMD habla sobre la Zettascale y como pretenden alcanzar ese nivel dentro de unos 10 años. La Zettascale pretende generar, almacenar y procesar datos a nivel de zettaflops y zettabytes, un proceso de la que todavía estamos lejos de ver, pero esa carrera parece haber comenzado ya.

AMD traza el camino hacia el Zettascale, empaquetados 2D, 2.5D y 3D

AMD traza el camino hacia la computación a Zettascale: Habla del rendimiento del CPU y la GPU, la eficiencia, el empaquetado de chips, y otros datos.

AMD estuvo en el ISSCC 2023 para hablar sobre el futuro de la computación, donde habló sobre las próximas tendencias de rendimiento y eficiencia que son esperables en los próximos años.

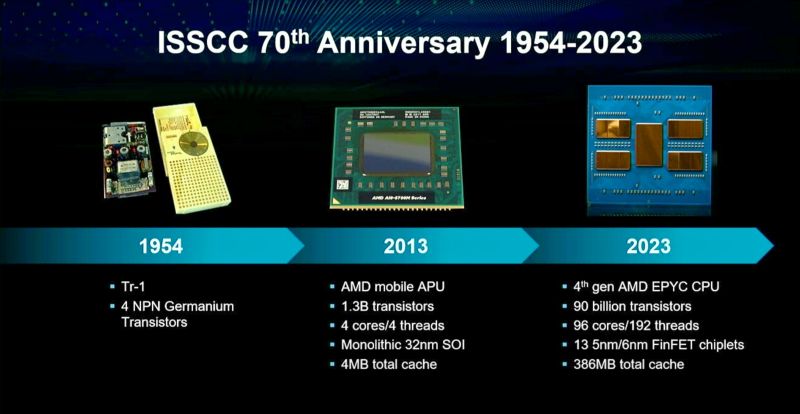

AMD hizo una pequeña retrospectiva sobre una de sus primeras APU ‘Richland’ que fue diseñada en el año 2013. En aquella época este chip poseía hasta 1,3 mil millones de transistores, 4 núcleos, 4 hilos, un proceso SOI monolítico de 32 nm y 4 MB de caché. 10 años después, AMD esta fabricando procesadores como EPYC Genoa de cuarta generación, la cual cuenta con hasta 90.000 millones de transistores, 96 núcleos y 192 hilos, nodos de proceso de 5 y 6 nm con 386 MB de caché.

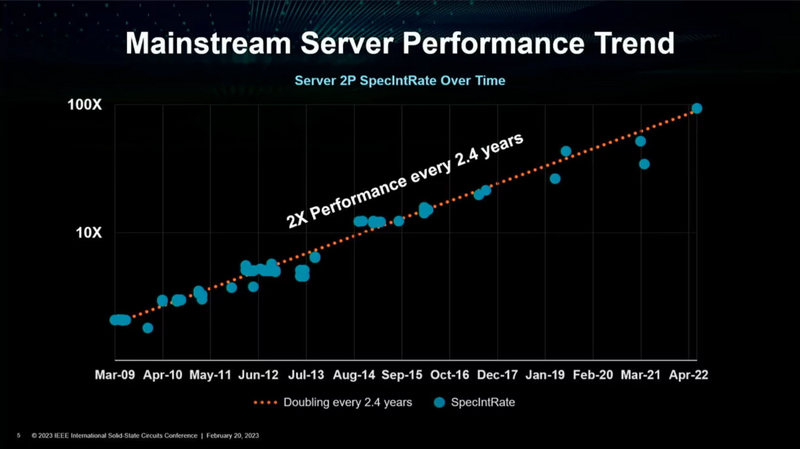

La industria ha estado mejorando el rendimiento de servidores principales cada 2,4 años. Mientras tanto, las GPUs han duplicado su rendimiento cada dos años. AMD ha sido el primero en superar la barrera de Exascale gracias a EPYC y el supero-ordenador Frontier, y ahora la meta es romper la barrera del Zettascale.

Te recomendamos nuestra guía sobre los mejores procesadores del mercado

Según las estimaciones de AMD, alcanzar el Zettascale tardará algo más de 10 años, con una eficiencia de 2140 GF/Watt consumiendo unos 500MW de energía utilizando las actuales tecnologías.

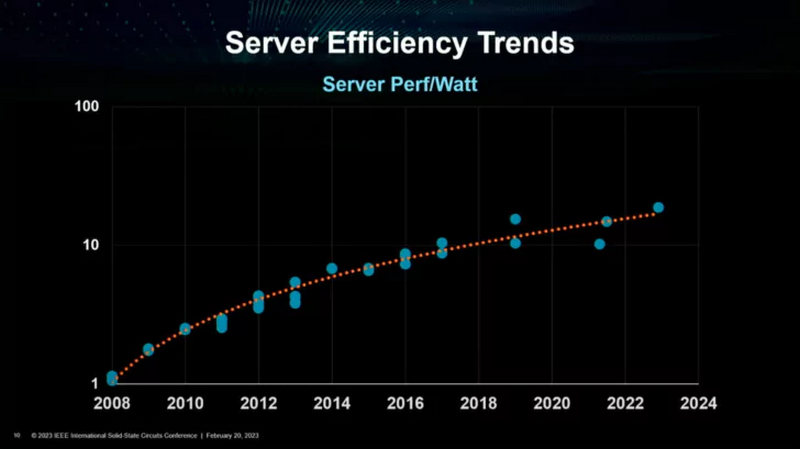

Uno de los grandes problemas para alcanzar el rendimiento en Zettascale, según AMD, es que el progreso de la eficiencia de la CPU y la GPU está empezando a aplanarse, así que para alcanzar esta meta tendrá un costo en la eficiencia.

Es por eso que AMD ha recurrido a tecnologías de chips apilados y empaquetados, algo que realizo con sus tarjetas Instinct y en EPYC Genoa. Los chips apilados y empaquetados juntos están ayudando a reducir el coste relativo de Bits/Joule.

En esta dirección, AMD prepara sus Instinct MI300, donde la caché y la estructura están en la parte inferior y los núcleos de CPU y GPU están apilados en 3D encima, junto con la integración 2,5D de la memoria y la estructura de interconexión. Todo esto contando con una arquitectura APU de memoria unificada. Todo está pensado para mejorar la eficiencia.

Gracias a este tipo de arquitectura del MI300, AMD podría multiplicar por 30 la eficiencia de aquí al año 2025.

En el área de empaquetado y chiplets, AMD también se propone una integración cada vez más estrecha de computación y memoria con alrededor de 0,2 pj/bit y diseños PIM (Processing-In-Memory) que reducirán la energía de acceso hasta en un 85%.

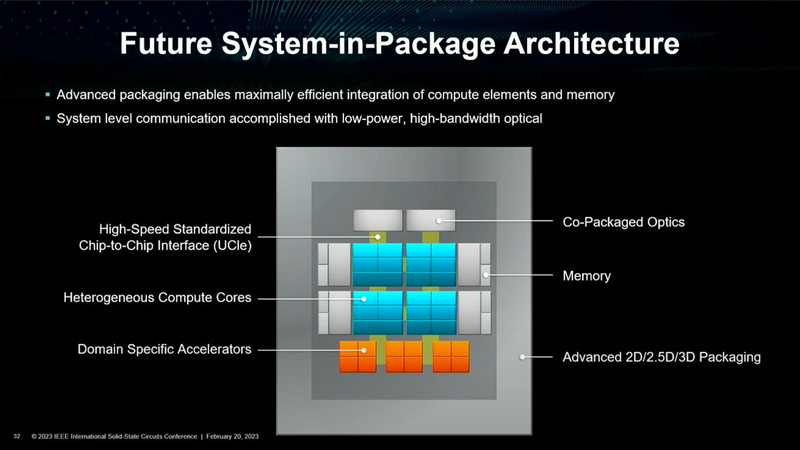

Por último, AMD mostró un nuevo empaquetado de chips que tiene pensado para el futuro, donde se combinan tecnologías de empaquetado 2D, 2.5D y 3D con una serie de aceleradores específicos de dominio, núcleos de cálculo heterogéneos, interfaz chip a chip de alta velocidad (UCIe), capas de memoria y mucho más. En definitiva, realizar chips cada vez más complejos tratando de aprovechar al máximo el espacio con múltiples chiplets y sistemas multicapa/apiladas con una combinación de fabricación 2D, 2.5D y 3D.

Gracias a esta nueva forma de crear chips de AMD, se espera que puedan alcanzar el Zettascale con 10.000 GFLOPs/Watio en una capacidad de 100MW, mucho menos que los 500MW de las tecnologías existentes. Pueden ver el informe completo en el siguiente enlace.