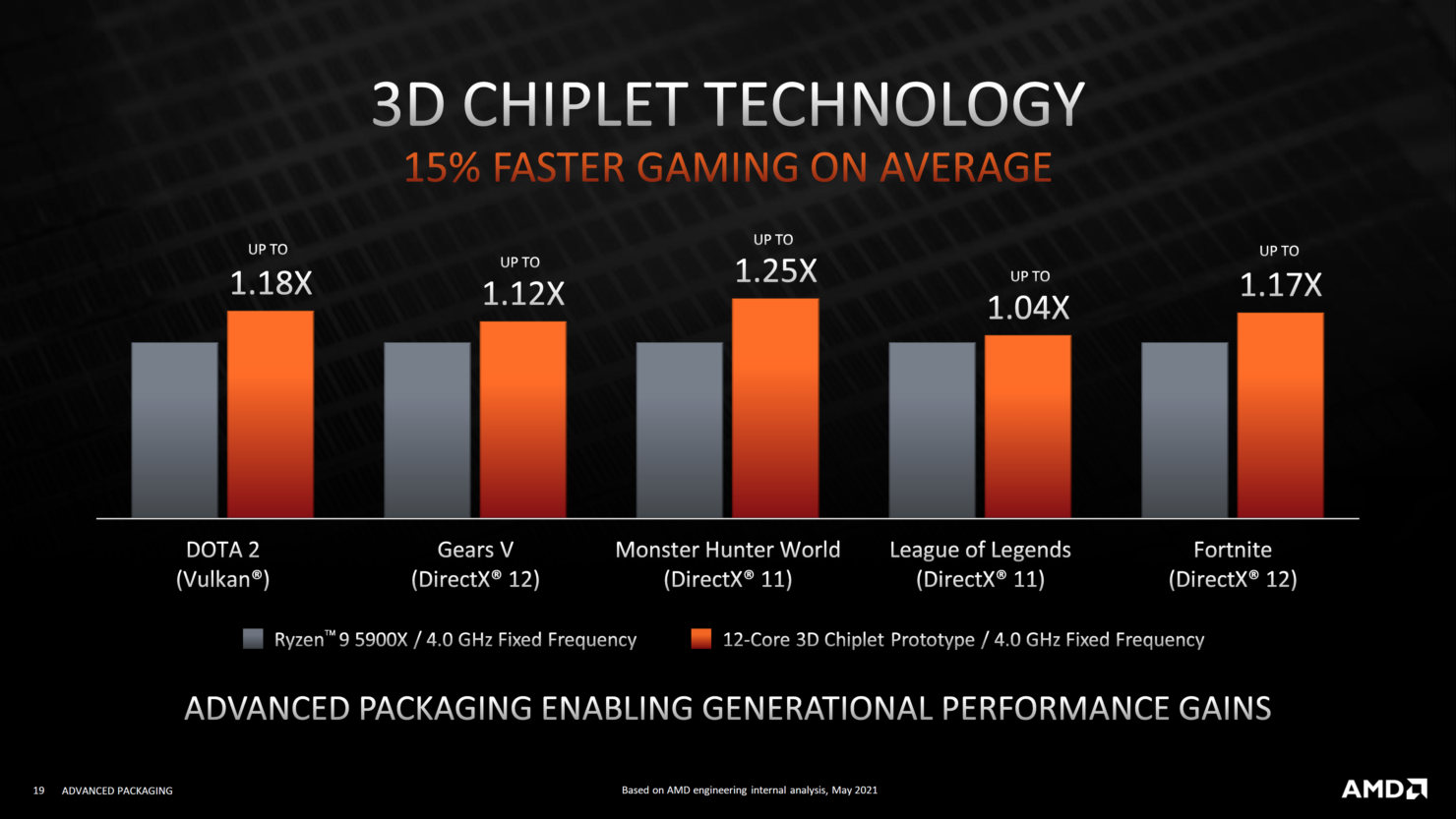

AMD publica una serie de diapositivas donde explica en detalle su próxima tecnología de chiplets multicapa, que se van a implementar en la serie de CPUs Ryzen 3D V-Cache.

AMD 3D V-Cache: Se revela su diseño de apilamiento 3D, aportará 15% más de rendimiento en juegos

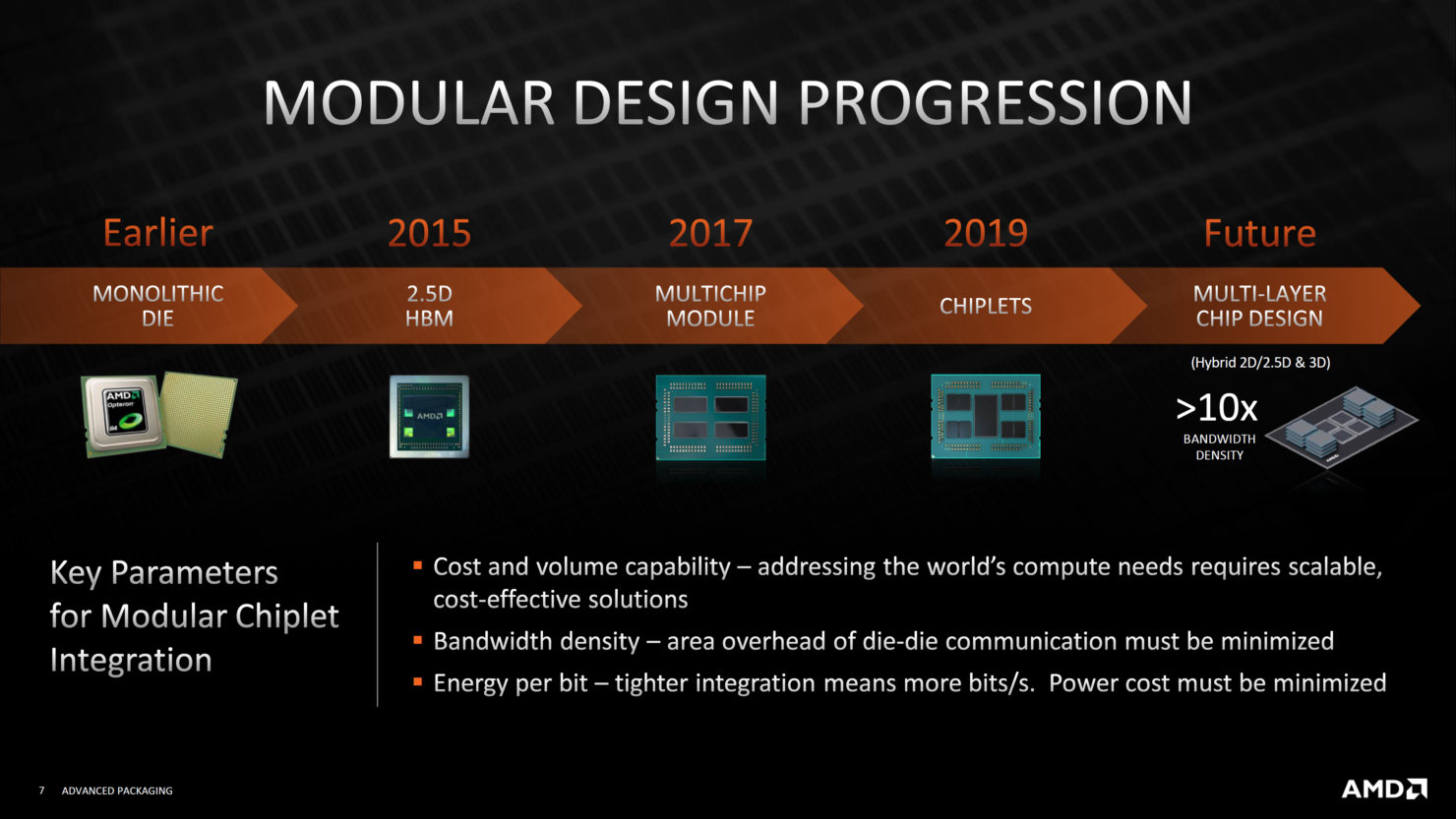

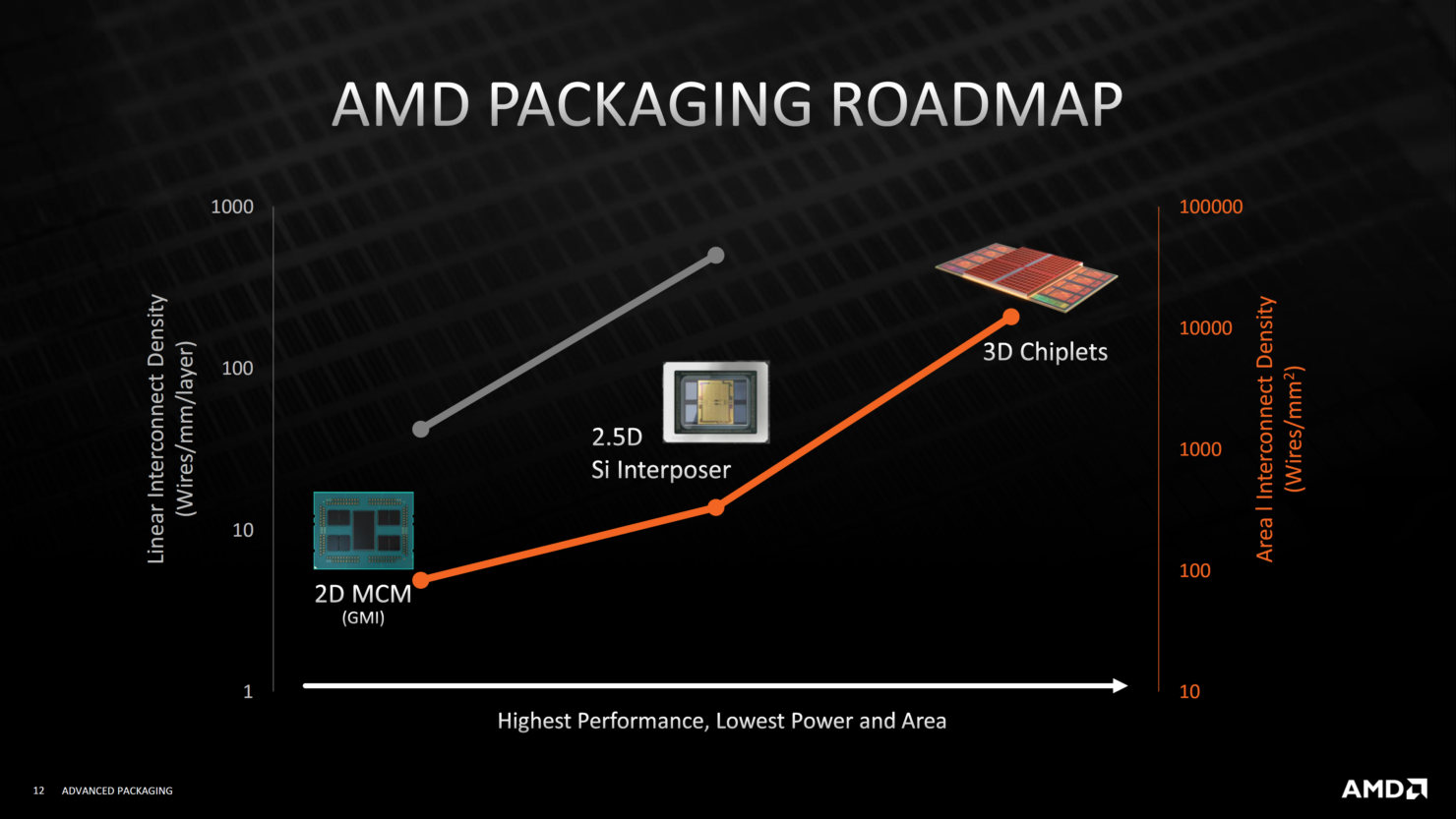

AMD ha dado más detalles sobre sus futuras tecnologías de diseño de chiplets multicapa que se integrarán próximamente, como los próximos chips Zen 3 con tecnología 3D V-Cache. En ellas se dan muchos detalles del actual diseño, el futuro de los chiplets híbridos 2D, 2.5D, 3D y la ganancia de rendimiento que se puede experimentar en juegos con respecto a la actual generación Ryzen 5000.

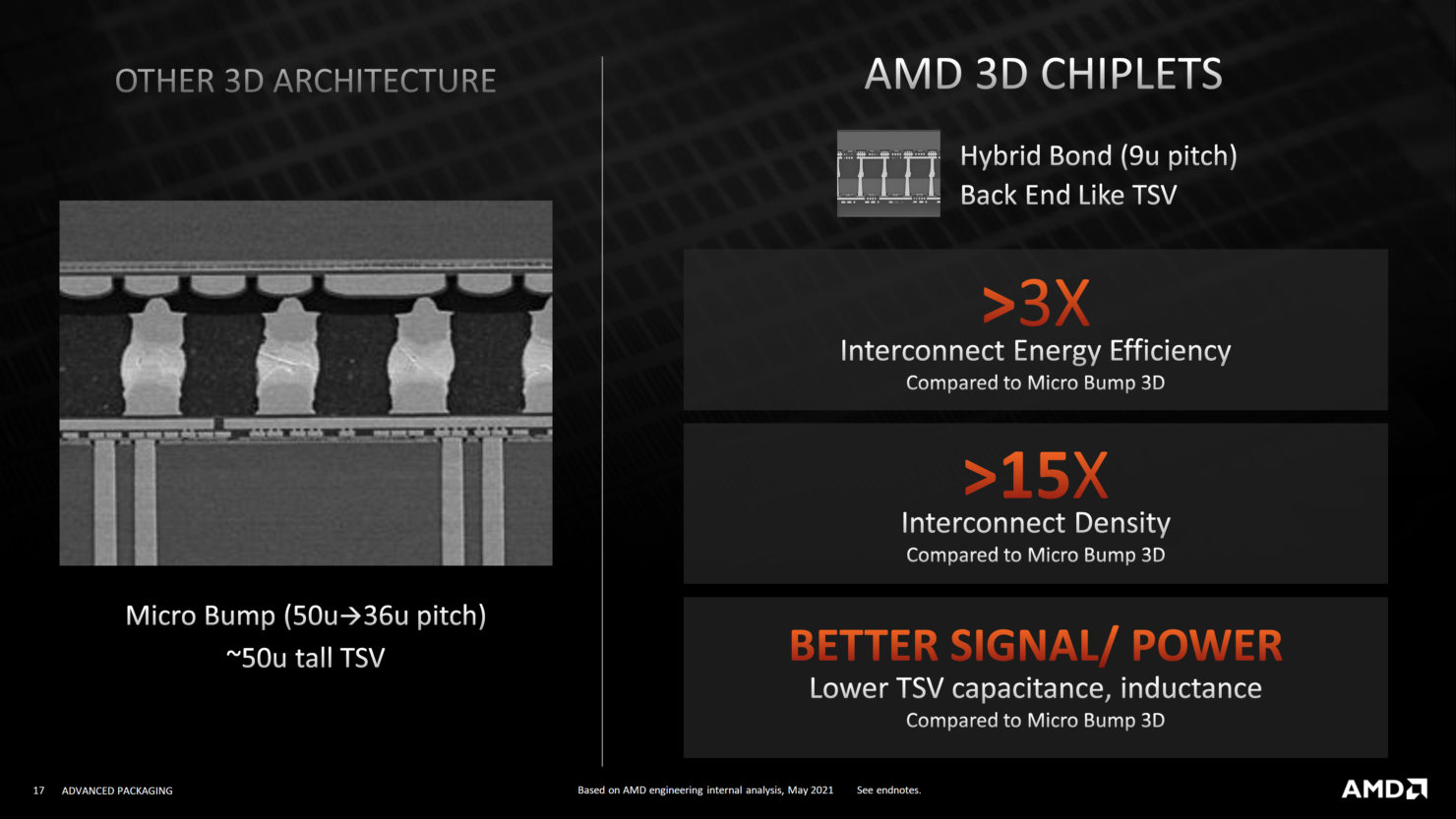

El año 2021 marcará el inicio de la arquitectura Chiplet 3D y con 3D V-Cache vamos a entrar por fin en el terreno del apilamiento 3D, en el que el núcleo Zen 3 de AMD contará con una cache SRAM sobre el CCD principal. Esto hace aumentar la densidad de interconexión con la utilización del Micro Bump (3D) y varias interconexiones TSV. La interconexión utiliza un nuevo enlace dieléctrico-dieléctrico con enlace Direct CU-CU que fue diseñado y co-optimizado en colaboración con TSMC.

El enlace híbrido tiene un paso de 9 micras con un extremo posterior similar al TSV. Estas interconexiones son que es ligeramente más pequeño que la interconexión Forveros de Intel, que tiene un paso de 10 micras. Además, esto aumenta la densidad de las interconexiones en hasta 15 veces y unas 3 veces en mejora de la eficiencia.

Visita nuestra guía sobre los mejores procesadores del mercado

En el futuro, AMD espera aprovechar la tecnología de apilamiento 3D para apilar núcleos sobre núcleos, IP sobre IP y otro tipo de configuraciones, por lo que esto es solo el principio.