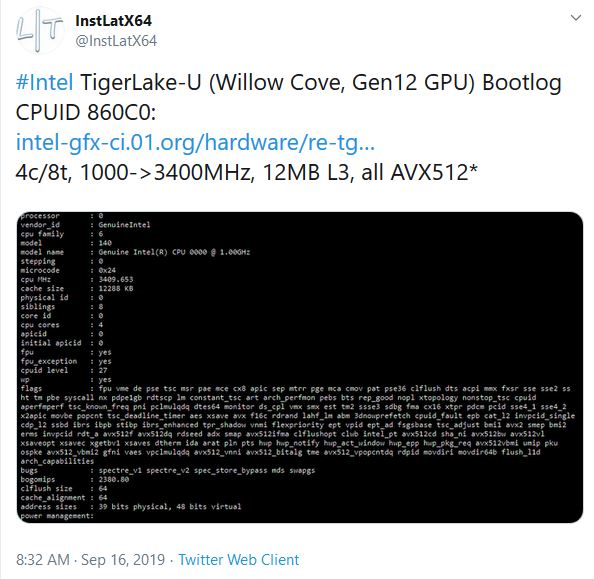

Tiger Lake-U presentará un aumento del 50% en la capacidad de caché L3, que pasará de 8MB a 12MB, por la publicación de un volcado de procesador por parte de @InstLatX64 en Twitter. Esto significa un aumento de hasta 3MB de caché L3 por núcleo.

Tiger Lake-U presentará un aumento del 50% en la capacidad de caché L3

Como era de esperar, el modelo Tiger Lake-U es un procesador de 4 núcleos con HyperThreading. La imagen publicada también revela que la muestra de ingeniería funciona a 3.4GHz, una frecuencia respetable para un modelo de pre-producción.

La imagen también contiene un montón de banderas que representan los conjuntos de instrucciones soportados. Confirma el soporte de AVX-512 como Sunny Cove, pero no parece tener la bandera avx512_bf que se esperaría si hubiera soportado bfloat16 como los procesadores Cooper Lake Xeon de principios del próximo año.

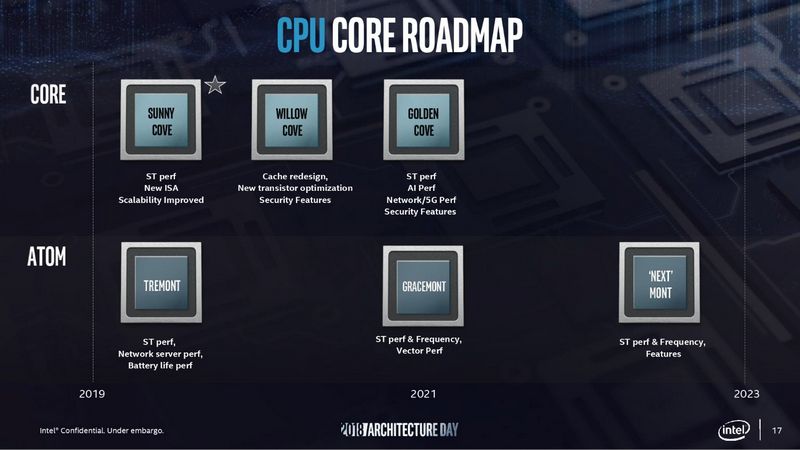

El volcado muestra que el Tiger Lake-U de cuatro núcleos tiene 12MB de caché L3 total, un aumento del 50%. Esto encaja con el rediseño de caché que Intel había revelado para Willow Cove, el núcleo de CPU de Tiger Lake, aunque es probable que el rediseño de caché implique cambios mayores que un simple aumento de tamaño. Por ejemplo, una caché más grande tiene una latencia más alta, por lo que es probable que haya algún ajuste más bajo el capo.

[irp]Tiger Lake está listo para ser lanzado el próximo año. Estos procesadores también contarán con los gráficos integrados Gen12 ‘Xe’, que tendrán una nueva función de visualización y una gran actualización del conjunto de instrucciones. Os mantendremos informados.