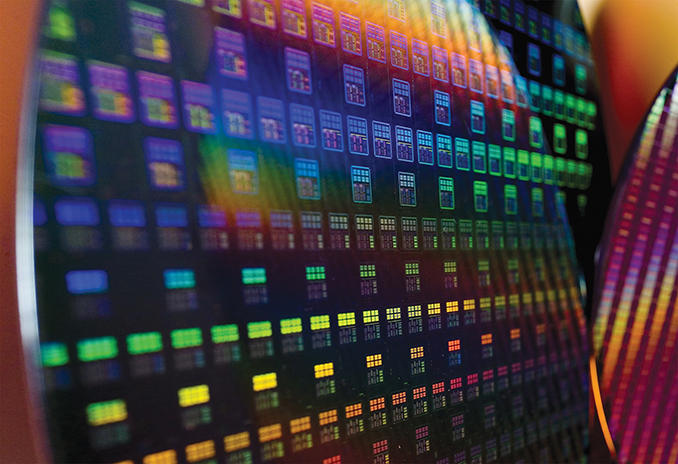

El nuevo proceso de fabricación a 7nm FinFET (CLN7FF) de TSMC ha entrado en la fase de producción en masa, con ello a fundición ya está planificando su hoja de ruta del proceso a 5nm, que espera tener listo en algún momento en 2020.

TSMC habla de las mejoras de su proceso a 5nm, el cual se basará en tecnología EUV

5nm será el segundo proceso de fabricación de TSMC en utilizar la litografía EUV (Extreme UltraViolet), la cual permite impulsar incrementos enormes en la densidad de transistores, con una reducción de área del 70% en comparación con 16nm. El primer nodo de la compañía en usar la tecnología EUV será el de 7nm + (CLN7FF +), aunque EUV se usará con moderación para reducir la complejidad en su primera implementación.

Te recomendamos la lectura de nuestro post sobre La arquitectura AMD Zen 2 a 7 nm se presentará este mismo año 2018

Esto servirá como una fase de aprendizaje de cara al uso de EUV en gran medida en el futuro proceso a 5 nm, el cual ofrecerá una reducción del 20% en el consumo de energía con el mismo rendimiento, o una ganancia de rendimiento del 15% con el mismo consumo de energía, respecto a los 7nm. Donde si habrá grande mejoras con los 5nm, es en la reducción del área de un 45%, lo que permitirá colocar un 80% más de transistores en la misma unidad de área que con los 7nm, algo que permitirá crear chips extremadamente complejos con tamaños mucho más pequeños.

[irp]TSMC también quiere ayudar a los arquitectos a alcanzar mayores velocidades de reloj, para ello ha declarado que un nuevo modo de «Voltaje de Umbral Extremadamente Bajo» (ELTV) permitirá que las frecuencias de los chips aumenten hasta en un 25%, aunque el fabricante no ha entrado en grandes detalles sobre esta tecnología o a qué tipo de chips puede ser aplicada.