La memoria HBM ha llegado como una buena alternativa a la DRAM tradicional, consiguiendo mayores anchos de banda para aplicaciones como la IA o la GPU. Sin embargo, muchos no conocerán la memoria HMC del HMCC, que fue la gran «perdedora» en su batalla contra la HBM. Aquí te hablaremos de ella…

Índice de contenidos

La necesidad de una nueva memoria

El cuello de botella entre la CPU y la RAM es un tema ya bien conocido. Y un gran problema y quebradero de cabeza para los ingenieros que buscan mejorar el rendimiento de los ordenadores actuales. Sin embargo, se trabaja mucho para tratar de crear nuevas tecnologías que puedan mejorar este problema, ya que la CPU y la RAM trabajan juntas y la unidad de procesamiento depende de ella para alimentarse con instrucciones y datos. Por tanto, si la RAM no alimenta a tiempo a la CPU, de poco sirve que ésta sea la más rápida…

El cuello de botella CPU-RAM surge principalmente debido a las siguientes razones:

- Velocidad de la RAM: la velocidad de la RAM, medida en MHz, determina la rapidez con la que los datos pueden ser leídos y escritos. Si la RAM es demasiado lenta, la CPU tendrá que esperar más tiempo para obtener los datos necesarios, lo que reduce el rendimiento. Sin embargo, no es sencillo subir la frecuencia de reloj de la memoria sin afectar a otros factores, como la temperatura, el consumo o la propia consistencia.

- Latencia de la RAM: se refiere al tiempo que tarda la RAM en responder a una solicitud de la CPU. Una latencia alta puede causar retrasos significativos en la ejecución de las instrucciones. Mejorar la latencia implicaría empeorar otras cosas, o lo que es lo mismo, tratar de mejorar otros aspectos importantes de la RAM significa empeorar la latencia.

La latencia CL (CAS Latency) es un parámetro crucial en la memoria RAM que indica el tiempo que tarda en acceder a un dato una vez que se ha enviado la solicitud. A pesar de ser una tecnología más reciente, la DDR5 presenta generalmente una latencia CL mayor que la DDR4, como sabrás. El motivo de esto es la nueva modulación de señales para aumentar el ancho de banda, que también es importante para mejorar el rendimiento, y en lo que cada nueva generación de DDR prioriza.

Esta limitación entre la CPU y la RAM puede manifestarse de diversas formas, como en un bajo rendimiento general, ralentización de la multitarea, o en una baja tasa de FPS en gaming, entre otros problemas.

Mitigar estos problemas de bottleneck entre CPU-RAM pasa por aumentar necesariamente la capacidad, mejorar la velocidad, minimizar la latencia, y mejorar el ancho de banda para el acceso paralelo. Por ese motivo, se necesita buscar nuevos paradigmas o tecnologías de memoria, como algunas de las que ya hemos hablado, o como la propia HBM o la HMC…

¿Qué es la HBM?

Muy resumidamente, para ponernos en contexto, la HBM (High Bandwidth Memory) o Memoria de Alto Ancho de Banda es una tecnología de memoria DRAM diseñada para ofrecer un ancho de banda excepcionalmente alto, en comparación con la DDR tradicional. Se consigue esto mediante el apilado de los chips de memoria DRAM, consiguiendo mejoras considerables en el acceso.

Sin embargo, por el momento, dadas las limitaciones o precio de otras memorias, ninguna de ellas ha conseguido desplazar del todo a la DDR. Tan solo se ha utilizado para tareas específicas, como los aceleradores de IA, algunas GPUs, o en HPC.

Para saber más sobre la HBM, puedes leer nuestro artículos

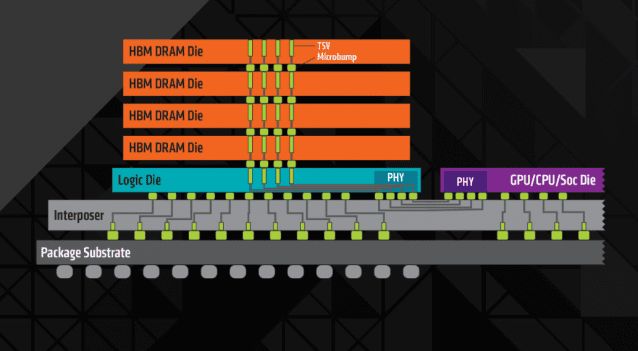

La HBM no estuvo sola: la propuesta de HMCC

HMC son las siglas de Hybrid Memory Cube, una nueva interfaz para una memoria tipo RAM de alto rendimiento basada en celdas DRAM. En este caso se apilan los chips DRAM y se conectan mediante TSV y microbumps, es decir, exactamente como en el caso de la HBM. Sin embargo, mientras la HMC tiene una lógica más genérica, la HBM es más específica, y se conecta mediante un interposer a la unidad de procesamiento a la que sirve.

HMC fue desarrollado por Samsung Electronics y Micron Technology en 2011. Prometía una mejora 15 veces superior sobre una DDR3. Para gestionar esta memoria, se puso en funcionamiento el HMCC o HMC Consortium, compuesto por Samsung, Micron, Open-Silicon, ARM, HP, Microsoft, Altera, y Xilin.

Se pueden apilar entre 4 y 8 chips DRAM uno encima de otro, con un controlador de memoria que está integrado como un chip separado. Cada pila se denomina cubo y se pueden encadenar hasta 8 cubos en una misma red enlazando cubo a cubo. Y los primeros chips presentados al público datan de 2013, con la especificación HMC 1.0, con bus serial full-duplex de 16 o 8 carriles en el que cada carril puede transferir de 10 Gbit/s hasta 15 Gbit/s. Y cada cubo típico con 4 enlaces tiene 896 pines GB, con un tamaño bastante compacto, de tan solo unos milímetros cuadrados.

Sumando el ancho de banda bruto de un enlace con 16 carriles con señalización de 10 Gbit/s se pueden obtener un total de 40 GB/s, 20 GB/s en cada sentido. Si tenemos un cubo con 4 enlaces, entonces se pueden alcanzar hasta 240 GB/s, o 120 GB/s transmitidos y 120 GB/s recibidos. Con un cubo de 8 enlaces tendríamos hasta 320 GB/s de ancho de banda…

La prueba mostrada estaba fabricada con chips DRAM bajo un nodo de 50nm y un chip lógico de 90nm con capacidad total para 512 MB, así como un voltaje de 1.2v y un consumo de energía de 11 W. En 2013 se consiguieron paquetes con hasta 2 GB por parte de Micron, con 4 matrices de memoria. Con la llegada de HMC 2.0, en 2014, las velocidades SerDes se ampliaron hasta los 30 Gbit/s, lo que permite que cada enlace pueda alcanzar por sí solo 480 GB/s, 240 en cada dirección.

Dadas estas cifras, algunos se interesaron en esta memoria. Uno de los primeros procesadores en utilizar memoria HMC fue el Fujitsu SPARC64 XIfx para el supercomputador japonés Fujitsu PRIMEHPC FX100 de 2015.

Sin embargo, la adopción no fue muy amplia, incluso menos que la que ha tenido HBM, con la que competía directamente. De hecho, sus principales fabricantes anunciaron en 2018 que se alejaban de la HMC en favor de la GDDR6 y la HBM, que eran más competitivas.

Te recomiendo leer sobre cómo funciona la memoria principal

¿Por qué se descartó la memoria HMC?

| Tipo de memoria DRAM |

DDR4 |

HMC |

HBM |

| Ancho de banda (Gbps/mm2) |

25.6 |

96 |

170.7 |

| Consumo de la interfaz (pJ/bit) |

20 |

2 |

1 |

Como sabes, JEDEC son las siglas de Joint Electron Device Engineering Council, una organización internacional que establece los estándares abiertos referentes a la memoria, tanto la RAM como la flash, entre otras tecnologías. Pero, mientras el HMCC es un consorcio que patentó la tecnología HMC y si alguien quería fabricarla tenía que pagar, el caso del JEDEC no es así, ya que cualquiera puede usar las especificaciones bajo JEDEC.

Lo que quiero decir con ésto es que HBM, aunque fue desarrollada por Samsung, AMD y SK Hynix, fue adoptada por JEDEC, convirtiéndola en un estándar abierto. Por tanto, otros fabricantes pueden fabricarla sin limitaciones. De hecho, la HBM aprovecha también algunas tecnologías de la JEDEC como es Wide I/O y Wide I/O 2 para este tipo de interfaces de memoria apilada.

Es por eso que al final HMC ha caído en el olvido, y HBM es la que ha terminado triunfando. A pesar de no ser mayoritaria, la HBM ha sido empleada en multitud de ASICs para IA, por muchos supercomputadores como el NEC SX-Aurora TSUBASA, y también para el Fujitsu A64FX basado en ARM, y que estovo como primero en el Top 500. También ha sido empleado por NVIDIA para algunas de sus GPUs dedicadas a IA, y por la AMD Fiji.

En definitiva, cuestión de dinero básicamente… algo parecido a lo que le ocurrió a la Rambus RIMM frente a la DDR, si lo recuerdas. Aunque es cierto que la HBM ha presentado algunas ventajas técnicas también.

¡Comenta!