Intel y TSMC han estado trabajando en un nuevo tipo de transistores llamados CFET (Complementary Field Effect Transistors).

CFET tendrá diseño de apilamiento, pudiendo añadir dos transistores en el espacio de uno

Una de las grandes particularidades de este transistor es que están apilados verticalmente. Este tipo de transistores están preparados para reemplazar a los transistores GAA ‘’gate-all-around’’ más tradicionales. Gracias a su diseño de apilamiento en vertical, se pueden añadir dos transistores en el espacio de uno, con todas las ventajas que ello conlleva.

El concepto de CFET data del año 2018, cuando fue presentado como un concepto por el instituto de investigación IMEC. Unos 5 años después, ese concepto a tomado forma hasta convertirse en una realidad, lo que aumentar notablemente la densidad de transistores de los chips.

Detalles técnicos

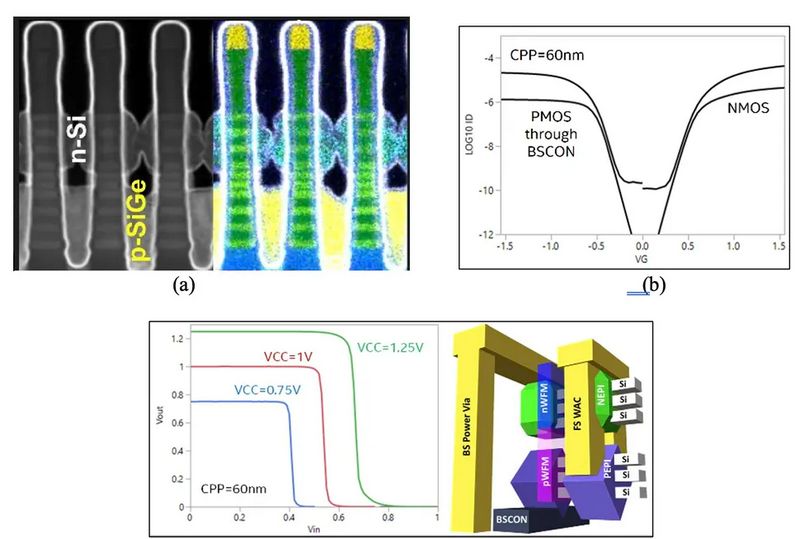

Se detalla que Intel ha logrado construir un CFET 3D monolítico, que incorpora tres nanoribbones n-FET superpuestos sobre tres nanoribbones p-FET, que es lo que podemos ver en la imagen. Es interesante la inclusión de un suministro de energía PowerVia en el transistor.

Mientras que Intel está diseñando estos transistores con una puerta de paso de 60 nm, TSMC lo hará con unos 48 nm. Los transistores diseñados por TSMC parecen haber superado el 90% de éxito en las pruebas de durabilidad, aunque estos transistores no estarían aplicando todas las características de CFET en este momento.

El nuevo transistor no solo aumentará la densidad de transistores, tambien permite tener un diseño más eficiente en términos de consumo eléctrico, la posibilidad de equilibrar las variaciones de los canales NMOS y PMOS, y por lo tanto un potencial de rendimiento mayor.

De momento, desconocemos cuándo se comenzará a implementar este tipo de transistores en los próximos chips.