Si has visto en algún lugar o has escuchado alguna vez RTL o Register-Transfer Layer, seguro que te has preguntado sobre qué es y para qué sirve este tipo de capa de abstracción. Pues bien, es algo vital a la hora de diseñar un circuito electrónico digital y aquí te mostramos todos los detalles que deberías conocer a cerca de ello.

Quizás también te puede interesar:

¿Qué es RTL?

A diferencia del diseño del compilador de software, en el que la capa de transferencia de registros es una representación intermedia, en los niveles inferiores la capa RTL es una entrada ordinaria sobre la que trabajan los diseñadores de circuitos. En el diseño de circuitos digitales, la capa de transferencia de registros (RTL) es la abstracción de diseño que modela el circuito digital síncrono en términos de las señales digitales (datos) que fluyen entre los registros de hardware, y las operaciones lógicas realizadas en estas señales. El nivel de transferencia de registros (RTL) es otro nivel de abstracción de diseño, que representa los circuitos digitales en un nivel superior en comparación con las abstracciones anteriores. Las abstracciones de nivel de transferencia de registros se utilizan en los lenguajes de descripción de hardware (HDL), como Verilog y VHDL, para construir representaciones de nivel superior de los circuitos, de las que se pueden extraer representaciones de nivel inferior y, finalmente, el cableado real.

Cuando se diseñan circuitos integrados digitales utilizando un lenguaje de descripción de hardware (HDL), el diseño se realiza normalmente en niveles de abstracción más altos en comparación con el nivel de transistor (familia lógica) o el nivel de puerta lógica. Cada diseño se realiza en el nivel de puerta utilizando una puerta estándar (véase la sección sobre circuitos digitales para más detalles). Niveles de abstracción de Verilog Verilog soporta diseños en un número de diferentes niveles de abstracción.

Utilizaremos una de las características del lenguaje Verilog que nos permite especificar un funcionamiento (qué) del diseño que puede ser interpretado por las herramientas de síntesis. Una de las razones para utilizar las técnicas de síntesis es la posibilidad de describir el diseño a un nivel de abstracción superior, en lugar de utilizar un montón de módulos instanciados, o de operadores binarios de nivel inferior, en asignaciones continuas. Esto significa que una asignación continua es una forma válida de describir los diseños para introducirlos en una herramienta de síntesis RTL. Esto nos permite ahora describir el diseño utilizando una lista de asignaciones continuas, una jerarquía de diseño o un bloque siempre.

Se puede apreciar fácilmente que el uso de un solo bloque always en el diseño de MUX_2 nos permite describir un diseño por su función, sin referencia a la implementación. Las declaraciones dentro del bloque always describen el diseño (o parte del diseño). Es posible que se quiera añadir código en la forma RTL que no aparezca en el diseño implementado.

Si implementamos un módulo RTL utilizando un enfoque no sintetizable, como las declaraciones de espera o las características de nivel superior de VHDL, entonces esto diferiría lo suficiente como para permitirnos probar el comportamiento del DUT. A diferencia del código de comportamiento, que se encuentra en un nivel de abstracción superior, los módulos RTL son más comúnmente sintetizables. El diseño RTL está mucho más cerca del diseño de comportamiento para los circuitos lógicos, ya que el diseño RTL modela el flujo de datos entre varios registros, y por lo tanto es mucho más intuitivo. El diseño RTL puede utilizarse para diseñar cualquier circuito digital, ya sea combinacional o secuencial.

Para qué se usa

El diseño a nivel RTL es la práctica típica de los diseños digitales contemporáneos. Para resolver las deficiencias mencionadas en el proceso de diseño de la lógica secuencial, y permitir a los diseñadores digitales desarrollar fácilmente circuitos de alta complejidad, se introduce una metodología de diseño RTL. Ciclo de diseño de circuitos con RTL El RTL se utiliza durante la fase de diseño lógico del ciclo de diseño de circuitos integrados. El diseño RTL convierte este trabajo de diseño a mano en un sencillo proceso automatizado en el que un diseñador puede escribir unas funciones para el diseño en un lenguaje de su elección, y la herramienta convierte todos sus diseños en los circuitos combinacionales y/o secuenciales equivalentes.

En lugar de diseñar el ASIC desde cero, lo que también requeriría la escritura de bibliotecas, el diseñador puede escribir la funcionalidad de esos circuitos en RTL, y generar una lista de red a nivel de puerta, que luego se utiliza para generar un diseño de circuito para el diseño ASIC. Este es un proceso automatizado; una herramienta tiene todas las definiciones de las bibliotecas estándar, que pueden manipular su correspondiente lista de redes a nivel de puerta, que es equivalente a su diseño RTL. Si abrimos la netlist independiente de la tecnología en Xilinx Vivado, podemos ejecutar sólo los pasos de diseño con el comando synth_design-rtl.

En la síntesis de circuitos, a veces se utiliza un lenguaje intermedio entre una representación de nivel de transferencia de registro de entrada y un netlist de destino. Si hay más de un registro de entrada, la información binaria puede transferirse a través de un sistema de comunicación llamado bus. La capa de transmisión de registros se compone principalmente de unidades de función, que almacenan datos o los manejan de alguna manera, y de enlaces de comunicaciones que conectan esas unidades de función.

Supongamos que un sistema digital transfiere información de un registro R1 a un registro R2 en varios momentos y bajo varias condiciones. El circuito de nube define en qué momento y con qué condiciones lógicas se produce la transferencia de los registros R1 a R2. Los diseñadores suelen utilizar un circuito de nube para implementar ciertas funciones booleanas, siendo la salida de ese circuito una señal de transferencia.

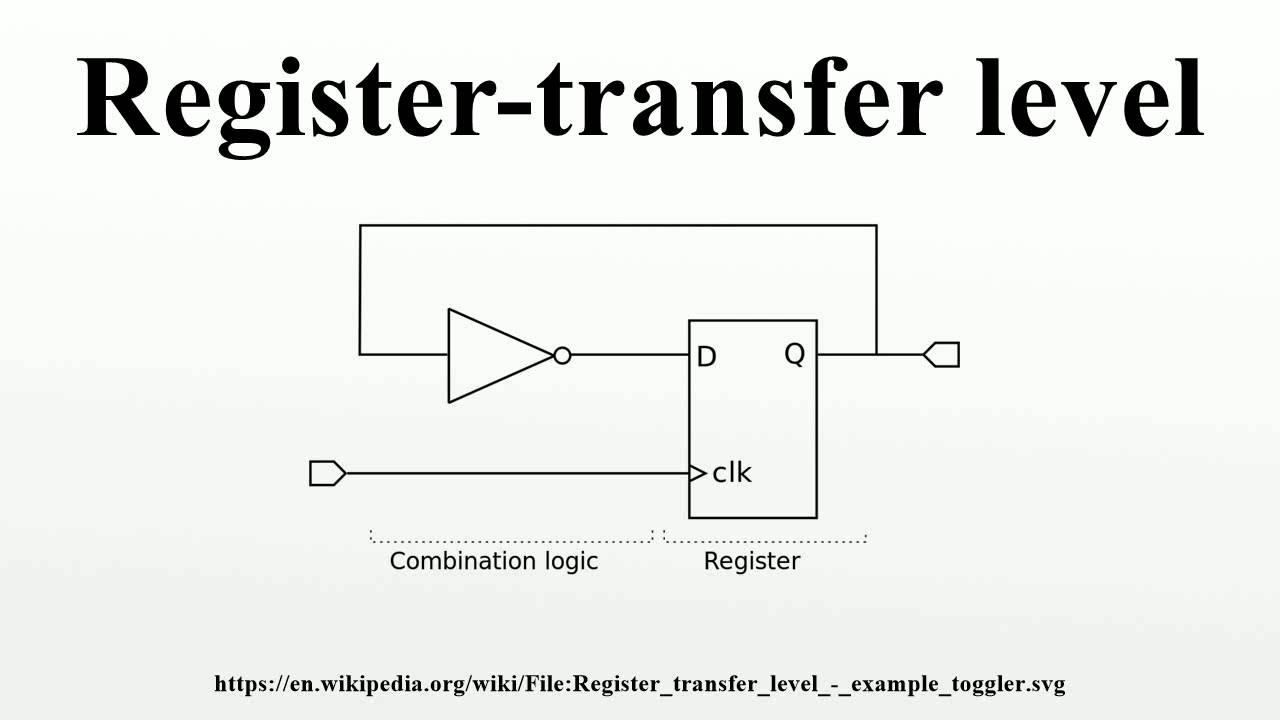

En los circuitos integrados, en los que todos los registros trabajan con el mismo número de bits, basta con tener este tipo de circuito de registro tan básico. En los esquemas de los circuitos integrados, los registros pueden representarse utilizando varios tipos de diagramas de bloques, como en la imagen siguiente.

En la metodología de diseño RTL, varios tipos de registros como contadores, registros de desplazamiento, SIPOs (Serial Input Output parallel), PIPOs (Parallel Input Serial Output) se utilizan como bloques de construcción básicos de cualquier circuito lógico secuencial. El término RTL se centra en la descripción de los flujos de señales entre los registros. El nivel de detalles de la RTL incluye la forma en que los datos se mueven entre los registros cuando el tiempo pasa de un flanco de reloj a otro. La capa de transferencia de registros El diseño mediante la capa de transferencia de registros especifica las características de un circuito mediante operaciones y transferencias de datos entre registros.

La existencia de bloques de funciones en una descripción RTL hace que la complejidad del diseño arquitectónico sea mucho más manejable, incluso para chips de gran tamaño, ya que la capa de registro-transferencia (RTL) tiene una granularidad suficiente para ser mayor que las descripciones a nivel de puerta o de circuito. Los códigos RTL también son aplicables a la lógica combinacional pura: No es necesario utilizar registros. Un circuito digital alternativo puede ser implementado con la escritura de un pequeño trozo de código, aumentando rápidamente el tamaño de la ruta de datos y el número de conexiones de entradas y salidas, haciendo que la lógica de control utilizando el diseño RTL, no requiera ningún esfuerzo en el diseño a nivel de puerta/circuito.