Seguramente que cada vez escuches más el término 3D packaging, y es que va a cobrar gran importancia conforme pasa el tiempo. Ya se han comercializado los primeros empaquetados 3D, como es el caso de AMD y su 3D V-Cache. En este artículo comprenderás algo más sobre estos tipos de empaquetados y su relevancia.

Índice de contenidos

¿Qué es un 3D Package?

Los chips empaquetados están dispuestos en la placa de circuito, conectados entre sí por pequeños cables. En todos los tipos de empaquetado 3D, los chips dentro de un paquete se comunican utilizando una señal fuera del chip, casi como si estuvieran montados en paquetes separados en una placa de circuito normal. Las CPUs 3D, las memorias HBM y otros chips de Intels utilizan minúsculos microbobinas de cobre como disposición de interconexión dentro del paquete, junto con el proceso de volteo del chip.

Una técnica denominada Hybrid Binding apila y conecta los chips utilizando diminutas interconexiones de cobre a cobre, lo que proporciona una mayor densidad y rendimiento que los actuales esquemas de interconexión de chips apilados. La unión híbrida de cobre, un proceso relativamente nuevo que se realiza en la planta de fabricación de semiconductores, es una tecnología puntera de apilamiento de chips que promete ofrecer a los clientes de chips algunas ventajas competitivas. La primera oleada de chips que salen al mercado con esta tecnología, denominada «hybrid bonding», prepara el terreno para una nueva y competitiva era de productos de chip basados en 3D y envases avanzados.

AMD ha sido el primer proveedor que ha introducido chips con unión híbrida de cobre, una tecnología de vanguardia para el apilamiento de troqueles que permite la próxima generación de dispositivos y paquetes de tipo 3D. Esta tecnología, denominada «hybrid bonding», ofrece a los diseños de gama alta unas cuantas opciones nuevas, que abren el camino hacia la próxima generación de diseños 3D, troqueles o matrices de RAM en 3D y envases aún más avanzados. La unión híbrida es una tecnología clave que resulta valiosa en la unión entre obleas y es igual de atractiva en la unión entre troqueles.

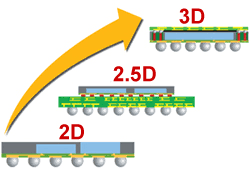

En este caso, la tecnología de interconexión dicta cómo se apilan las matrices y se unen en paquetes. En un circuito electrónico tradicional en 2D, cada matriz se empaqueta por separado. Las pilas de matrices en los chips 3D están mucho más cerca que las de un circuito impreso.

Particularidades

El chip tiene que diseñarse teniendo en cuenta el apilamiento de las matrices y se necesita maquinaria especializada para alinearlas y unirlas. En primer lugar, cada matriz de una pila debe diseñarse teniendo en cuenta el apilamiento, y este esfuerzo de diseño es importante. De hecho, las pilas de varios troqueles pueden incluir combinaciones que simplemente no son posibles de realizar en chips 2D.

En lugar de aplanar un conjunto (por tanto, 2D) de chips en matrices interconectadas horizontalmente, cada una de ellas contenida en su propio minúsculo paquete o caja, para protegerla de los efectos corrosivos, las tecnologías más sofisticadas ahora colocan los chips en capas verticales (por tanto, 3D) en una única caja igualmente pequeña, cuyo contenido constituye todo el sistema. En la actualidad, la industria utiliza las técnicas de embalaje más avanzadas para encajar varios chips de alto nivel y/o maduros en un solo envase, lo que también se conoce como integración heterogénea.

Las foundries responden a las nuevas necesidades

A medida que los chips se vuelven más y más complejos, las técnicas avanzadas de empaquetado son un área potencial de grandes avances tecnológicos. Se espera que las tecnologías innovadoras de empaquetado e interconexión de chips con múltiples troqueles sean fundamentales para los procesadores de vanguardia en los próximos años, por lo que todos los principales diseñadores y fabricantes de chips han desarrollado sus propios métodos patentados de empaquetado e interconexión de chips. Otros fabricantes de semiconductores por contrato (TSMC, GlobalFoundries), fabricantes de circuitos integrados (Intel, Samsung) e incluso desarrolladores de chips sin fábrica (AMD) que pueden acceder a las herramientas de fabricación y tecnologías de proceso más recientes también están desarrollando sus propios métodos de empaquetado e interconexión de chips en 2,5D y 3D para ofrecerlos a sus clientes o a sus propios productos futuros.

Estas empresas no pueden acceder a las herramientas de fabricación necesarias para producir chips con técnicas de fabricación por debajo de los 10 nm y, por tanto, los métodos avanzados de empaquetado e interconexión también son fundamentales para los SMIC. Varios fabricantes de chips, incluido el competidor de Intel, TSMC, disponen de este tipo de tecnología de empaquetado en 3D.

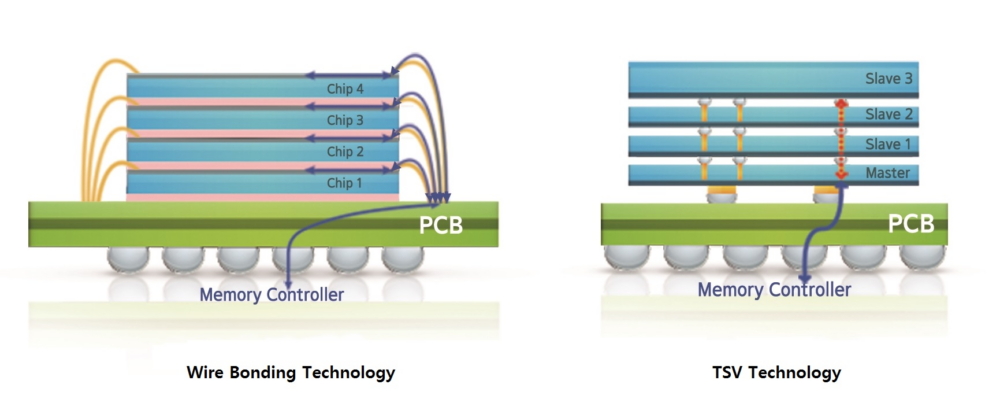

Un objetivo y distintos métodos

En función de las tecnologías, el mercado del embalaje de semiconductores en 3D se divide en agujeros pasantes de silicona en 3D, paquetes en 3D sobre paquetes, bases de abanico en 3D, enlaces de alambre en 3D y otros. Una de las formas de segmentar el mercado de empaquetado se basa en los tipos de interconexión, que incluyen la unión de cables, el flip-chip, el empaquetado a nivel de oblea (WLP) y la vía-silicio-vía (TSV).

Entre los ejemplos de empaquetado en 3D se encuentran el empaquetado en paquete (POP), en el que las matrices individuales se empaquetan, los paquetes se apilan y las interconexiones se forman mediante un proceso de wirebond o flip-chip; y el empaquetado en 3D a nivel de oblea (3D WLP), en el que se utilizan capas de redistribución (RDL) y un proceso de bumping para formar las interconexiones. Aunque se está buscando una mayor densidad de empaquetado, muchos de estos dispositivos siguen basándose en tecnologías más antiguas, como los wire bonds y los flip chips.

Los tamaños más pequeños y el menor consumo de energía son los principales factores que impulsan la demanda de chips con diversas técnicas avanzadas de empaquetado de semiconductores, una de las cuales son los diseños de empaquetado tridimensional. El empaquetado tridimensional permite a los diseñadores de chips utilizar las caras baldosas producidas con tecnología cuando son importantes, como el cerebro de los chips de los procesadores, y luego utilizar tecnologías más antiguas cuando la velocidad no es tan crucial, ahorrando costes. La nueva carrera de la fabricación de chips consiste en juntar chips -pequeños trozos cuadrados de lo que normalmente es un gran chip- apilados sobre una capa básica de silicio en un paquete, mezclando y combinando varias tecnologías en lugar de intentar construir un gran chip.

Intel ha dado algunos detalles de alto nivel sobre la nueva tecnología denominada Foveros, una tecnología de empaquetado en 3D que hará su debut en el producto el año que viene y que permitirá apilar directamente chips lógicos complejos y diversos uno encima de otro el año siguiente. Para ello, Applied Materials -la empresa que fabrica todas las máquinas que utilizan Intel, TSMC, Samsung, GloFo y todos los demás fabricantes de semiconductores Samsung- y el Instituto de Microelectrónica de A*STAR (IME) han anunciado la puesta en marcha de un laboratorio de empaquetado de chips en 3D de última generación en Singapur. La principal fundición de semiconductores de Taiwán está planeando una instalación en Estados Unidos para la producción de obleas, pero es la alianza japonesa la que cuenta cuando se trata de desarrollar tecnologías de empaquetado de vanguardia.

Para apoyarse, la innovación en el empaquetado de chips y en las tecnologías de interconexión de chips en general, así como el apilamiento en 3D en particular, es la forma en que Huawei puede empaquetar más transistores en sus SoC y lograr el rendimiento necesario para la competencia, dijo Guo Ping, un presidente rotativo retirado de Huawei, durante una reciente rueda de prensa, informa DigiTimes. Este tipo de chippacking en 3D está madurando rápidamente y es cada vez más relevante, ya que las características necesarias en las unidades más pequeñas que deben incluirse en un paquete, los trozos de la oblea llamados die, se reducen a 3 nanómetros y nodos más pequeños. En general, la integración 3D es un término amplio que engloba tecnologías como el empaquetado 3D a nivel de oblea; la integración basada en interpositores 2,5D y 3D; los CI 3D apilados (3D-SIC) y monolíticos 3D; la integración 3D heterogénea y la integración de sistemas 3D.

Futuro

Se espera que la tecnología de empaquetado de semiconductores en 3D se beneficie también de la disponibilidad de nuevos materiales de empaquetado, como las placas de circuitos impresos. Se espera que la necesidad de miniaturizar los chips de memoria, la necesidad de circuitos electrónicos de mayor ancho de banda y los requisitos de control de costes impulsen aún más la demanda de empaquetado de semiconductores en 3D. Se espera que la demanda de chips empaquetados en 3D aumente debido a las importantes inversiones en I+D de algunos de los principales actores, como Amkor Technology, ASE Group y Siliconware Precision Industries Co., Ltd., entre otros, que han permitido mejorar las técnicas de empaquetado de alta gama. Se espera que la tecnología de empaquetado en paquete (POP) en 3D experimente un mayor aumento, con los procesadores de aplicaciones que utilizan las innovaciones mejoradas que dependen de chips más pequeños, que son más rápidos para inspeccionar los paquetes de acuerdo con una configuración normal.

Te recomendamos la lectura de nuestra guía sobre los mejores procesadores.

Es probable que la creciente penetración de los dispositivos inalámbricos y del IoT aporte nuevas oportunidades y permita que esta tecnología impulse su cuota en el mercado de los envases de alta gama. Las ventajas tecnológicas del embalaje 3D Las ventajas del embalaje 3D están impulsando su demanda en aplicaciones de gama alta, como los chips utilizados en superordenadores, DRAMS, NAND, circuitos de microelectrónica, etc.