RISC-V ha llegado para quedarse. Hacía tiempo que no se diseñaba una nueva ISA. Las actuales arquitecturas se crearon hace décadas. Pero ahora todo ha cambiado, esta joven ha irrumpido con mucha fuerza. No es una arquitectura convencional, sino que es open-source, o de código abierto. Y, por el camino que está tomando, podría convertirse en «el Linux» del mundo de hardware, toda una revolución. Normal que algunos competidores han empezado a llamarla RISK-V, puesto que la ven como una seria amenaza…

Pero ¿qué es esta ISA? ¿qué la diferencia de las demás? ¿qué significa que sea open-source? ¿ya existen equipos basados en RISC-V? Vamos a tratar de disipar todas esas dudas y mucho más.

Índice de contenidos

El conjunto de instrucciones, repertorio de instrucciones, o ISA (Instruction Set Architecture), es una especificación detallada de todas las instrucciones (transferencia de datos, aritméticas, lógicas, de comparación, operaciones sobre bits, desplazamientos, control, saltos, etc.) que puede entender y ejecutar una CPU, además de los tipos de datos nativos que soporta, modos de direccionamiento de memoria, los registros y otros aspectos. Algunos ejemplos de ISA pueden ser AMD64, SPARCv9, AVR, ARMv8, RISC-V, Power ISA, z/Architecture, etc.

Estas ISAs pueden ser de varios tipos, aunque los más extendidos son CISC (Complex Instruction Set Computer) y RISC (Reduced Instruction Set Computer), siendo éste último el predominante en la actualidad debido a sus ventajas. Los tipos ya los detallaremos en otro artículo próximamente, por el momento, simplemente debes saber que RISC-V es de tipo RISC, como su propio nombre indica.

Los mnemónicos (lb, sb, sub, mul, add, div, or, xor, bne…) empleados para identificar a las instrucciones de una ISA, son los mismos que se emplean en el lenguaje ensamblador para esa arquitectura. Por ejemplo, este Hola Mundo en ASM de RISC-V:

# Programa en ensamblador para RISC-V sobre Linux para imprimir en pantalla un ¡Hola Mundo! .global _start #Dirección de inicio de programa para el linker #Configuración de parámetros para el Hola Mundo y la syscall() para Linux necesaria _start: addi a0, x0, 1 # 1 = StdOut la a1, Hola Mundo #Carga la dirección de Hola Mundo addi a2, x0, 13 #Longitud de nuestra cadena de texto a imprimir (13 caracteres: 12+1 por el salto \n) addi a7, x0, 64 #Selección de la syscall write() de Linux para imprimir el mensaje ecall #Llamada a la syscall de Linux para imprimir el mensaje en pantalla #Configuración de los parámetros de salida del programa addi a0, x0, 0 #Retorna 0 addi a7, x0, 93 #Código para la syscall terminado ecall #Llamada para terminar el programa .data helloworld: .ascii "¡Hola Mundo!\n" #Mensaje a imprimir

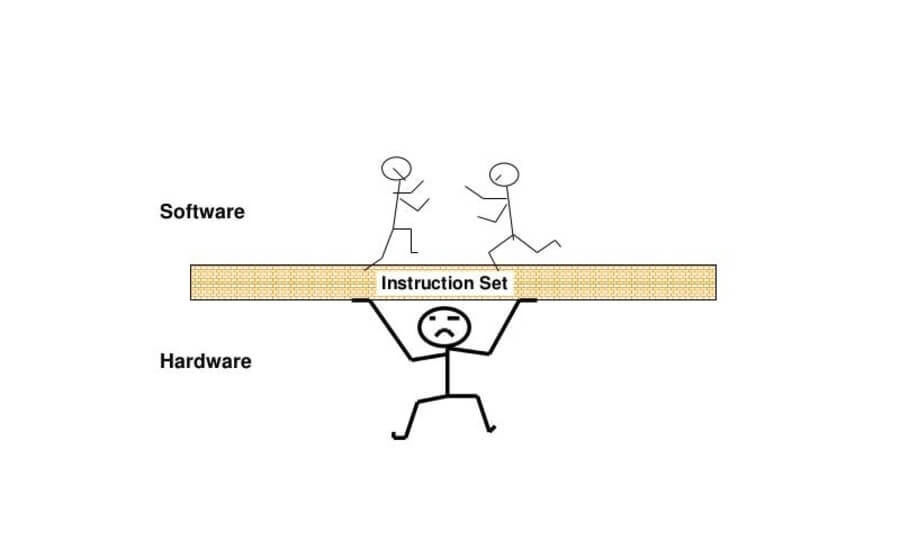

Como se puede apreciar en la imagen superior, la ISA es algo intangible que se encuentra entre la capa de software y la capa de hardware. La implementación de una ISA es la microarquitectura, y la implementación física es el chip resultante. Cuando se escribe un programa, el compilador creará un binario ejecutable, y éste a su vez incluye datos e instrucciones que se encuentran en la ISA. Así, una vez se carga en memoria y las instrucciones comienzan a entrar en la CPU, pueden ser interpretadas y procesadas. Por este motivo, un software compilado para una ISA no es compatible con otra, ya que la CPU no comprendería las instrucciones.

A finales de los años 70 los diseños CISC lanzados fueron bastante complejos, necesitando gran cantidad de transistores para su implementación. En 1979, David Patterson se tomó un año sabático de su trabajo en la Universidad de Berkeley para ayudar al equipo de DEC a mejorar el microcódigo de VAX. Al ver la complejidad concluyó que era insostenible.

De vuelta a Berkeley, Patterson iniciaría un proyecto en la universidad financiado por el DARPA VLSI Program, y rápidamente se opondría al concepto tradicional de más es mejor (CISC). Pensó que si el microcódigo era eliminado, podría ser incluso más rápido. Así es como surgiría el chip RISC-I. Éste sería más rápido con solo 1/3 de los transistores.

En 1981, en la Universidad de Stanford se inicia un proyecto similar, este proyecto era el MIPS, por John L. Hennessy. El primer sistema funcional se produciría en 1983, y los primeros programas pudieron comenzar a correr en él en 1984. MIPS enfatizaba en una agresiva frecuencia de reloj usando pipeline para hacer que corriese todo lo máximo posible.

A pesar de que ambos proyectos se realizaron casi en paralelo, la arquitectura tomó el nombre de RISC.

Tanto del RISC como de MIPS se fueron sucediendo numerosas versiones, como las MIPS I (1985), MIPS II (1989), MIPS III (1991), MIPS IV (1996), MIPS V (1998), MIPS32 (1999), y MIPS64 (1999). Pero lo que más importa aquí es la parte del proyecto RISC, aquel proyecto inicial finalmente sería abandonado (¿o no?):

Y el proyecto aparentemente desapareció, aunque su legado continuó en diseños RISC muy populares, como los DEC Alpha, SPARC, PA-RISC, AMD 29k, Power, Arm, MIPS, etc. Y de repente, en 2010 se inicia un proyecto comandado por Krste Asanović en Berkeley. Se reunió a un equipo para investigar sobre un sistema de código abierto y que terminó continuando el legado iniciado por Patterson, y denominado RISC-V.

RISC-V es una ISA de código abierto, lanzada bajo licencia BSD permisiva, lo que permite desarrollar implementaciones bajo cualquier licencia, ya sea también abierta o cerrada. Pero no solo destaca por eso, sino que también tiene otras ventajas interesantes, como ser una ISA diseñada recientemente, y pensando en las necesidades de la computación actual (IA, aceleradores específicos,…). Algo que el resto de ISAs no tienen, ya que fueron diseñadas en los años 80 en su mayoría.

Otro factor importante es su modularidad. Mientras otras ISAs son un «bloque» de instrucciones, la RISC-V permite usar el bloque de instrucciones que se necesite, haciendo que el procesador pueda ser más sencillo y eficiente. Todo lo contrario a la familia x86, que arrastran un problema mayúsculo debido a la retrocompatibilidad que mantienen. Entre los módulos de instrucciones que se pueden implementar en la microarquitectura están:

Me gustaría agregar que, no todas estas instrucciones se encuentran en la misma fase. Al ser una ISA tan moderna, algunas aún no han sido ratificadas. Por ejemplo, la RV32E y la RV128i aún están abiertas a cambios, mientras el resto están ya ratificadas y son estables, no cambiarán. Lo mismo ocurre con las extensiones, algunas ya ratificadas y otras no. En las especificaciones de RISC-V podrás comprobar su estado (ratificado, congelado, abierto).

Ratificadas: ya están cerradas, no se incluirán más instrucciones y han sido verificadas.

Congeladas: ya no se pueden hacer cambios, pero deben ser verificadas.

Abiertas: están aún abiertas a cambios.

Última actualización el 2025-02-26

Poco a poco RISC-V va centrando más miradas de la industria, y muchos grandes ya se han fijado en ella. Desde el IoT y otros embebidos RT, hasta PCs, pasando por HPC, y dispositivos móviles. La expectación no tiene precedentes, e incluso podría superar a Arm en un futuro próximo.

Algunas de las compañías que ya se han interesado en RISC-V son:

De hecho, el procesador europeo derivado del proyecto EPI que se está desarrollando, han empleado CPUs basadas en ARM y un acelerador basado en RISC-V.

Por último, debes saber que RISC-V es compatible con Linux, y que ya hay productos que puedes probar para hacerte una idea de cómo funciona esta ISA. La compañía SiFive, formada por algunos miembros implicados en RISC-V, tiene algunos de estos proyectos a la venta.

Última actualización el 2025-02-26

La SiFive Unmatched es una de las placas base más potentes que puedes probar, y con prestaciones realmente impresionantes. Aquí tienes un resumen de ellas:

También existen otros productos de hardware basados en RISC-V, aunque no tan ricos como la placa de SiFive, que es lo más parecido a una placa convencional para PC que podrás encontrar. Otras SBCs y placas de microcontroladores tipo Raspberry Pi y Arduino, son BeagleV, HiFive1 RevB, Seeed Studio Perf-V, SparkFun RED-V RedBoard, LoFive, etc.

Microsoft está intensificando su campaña para tratar de convencer a los usuarios para actualizar a…

AMD cree que la inferencia de la IA para smartphones y portátiles va a ser…

El chipset Intel Nova Lake-S debutaría con un nuevo tamaño, lo que haría necesario apostar…