Faltan datos por conocer de los procesadores Intel Sapphire Rapids, pero exploramos las posibles configuraciones de DIE basándonos en la tecnología EMIB. Destacar que la tecnología EMIB es fundamental para comunicar los diferentes DIE, así como comunicar estos con las memorias HBM2e.

Índice de contenidos

Qué es Intel EMIB

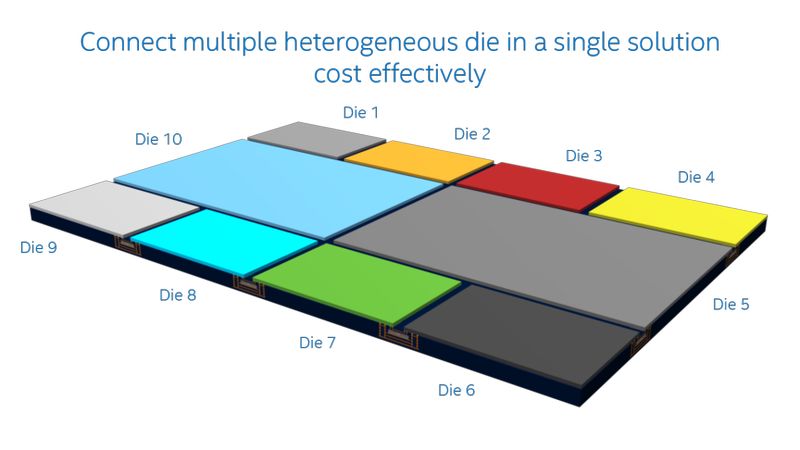

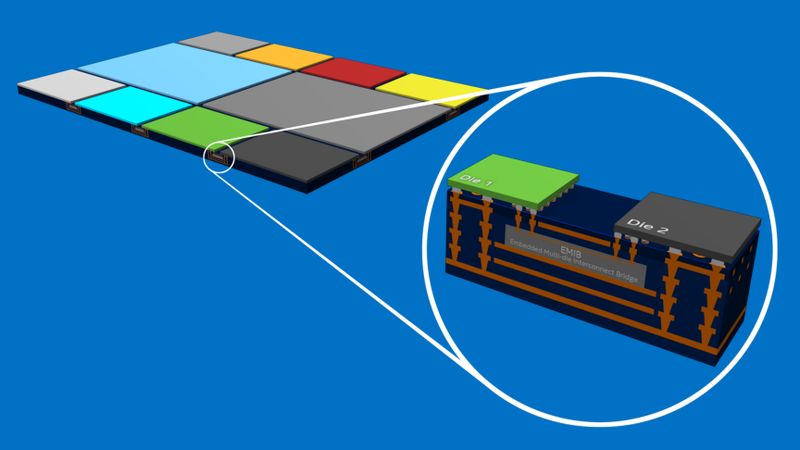

Es un sistema de interconexión de paquetes de alta densidad de configuraciones heterogéneas. Sencillamente, EMIB permite la interconexión de diferentes tipos de DIE que se puedan integrar en un encapsulado.

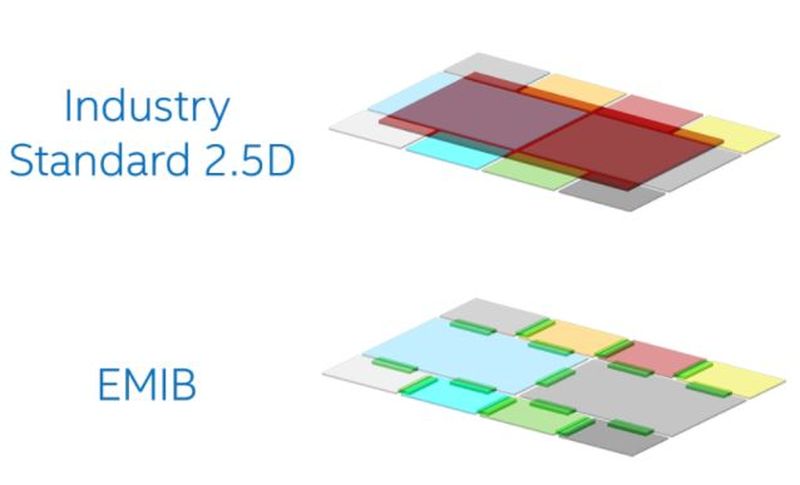

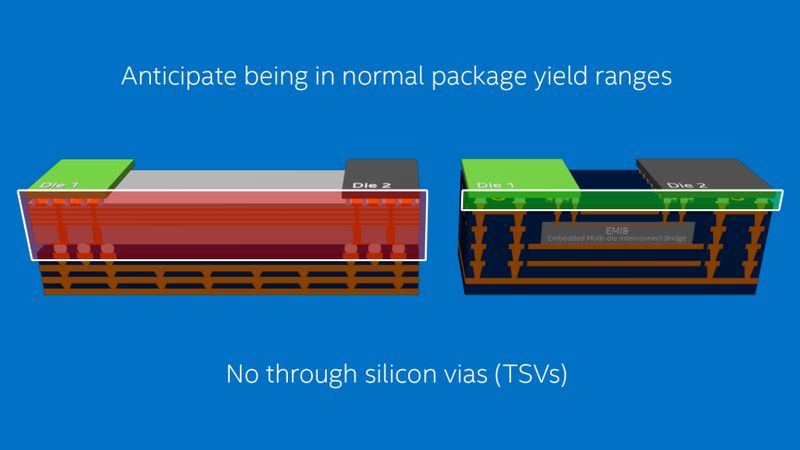

Habitualmente dentro de la industria se utiliza un interposer de silicio basado en la tecnología 2.5D. Todos los DIE del encapsulado deben estar encima de este interposer para poder comunicarse. Intel lo que hace es reducirlo a un puente que conecta únicamente los DIE contiguos. Además, este sistema de interconexión permite la creación de varias capas de enrutamiento. Dicho puente EMIB se incrusta en el proceso de fabricación del sustrato.

Conexión de chips heterogénea

Las técnicas de encapsulado actuales limitan el número máximo de conexiones entre DIE. Esta técnica se denomina como encapsulado 2.5D, haciendo uso de un interposer de silicio y varias vías de silicio (TSV) para interconectar los DIE. Dicho sistema establece una velocidad determinada en la interconexión, debido al limitado espacio.

El problema de este tipo de diseño es la complejidad. Crear este tipo de entramados es muy difícil y requiere de técnicas de fabricación avanzadas. Algo que puede generar retrasos en el desarrollo y/o lanzamiento de procesadores y que además, limita el rendimiento.

Integración de los puentes de interconexión

Durante bastante tiempo Intel ha buscado cambiar el empaquetado 2.5D, buscando algo que fuera fácil de diseñar, se acoplara a cualquier chip y se pudiera integrar con facilidad. El resultado de esta investigación ha sido EMIB.

Se pueden integrar un gran número de puentes en un mismo sustrato. Esto ofrece que existan una gran cantidad de E/S y una gran cantidad de rutas de interconexión eléctricas bien controladas. Algo que elimina la necesidad de un interposer de silicio con TSV, que puede terminar impactando en el rendimiento.

Para su desarrollo se utilizan microirregularidades para las señales de alta densidad y circuitos invertidos estándares de perfil grueso para las conexiones de alimentación directa y a tierra desde el chip hasta el encapsulado.

Simple y escalable

Los interposer tradiciones basados en el diseño 2.5D deben ser mucho más grandes que el tamaño de todos los DIE que se quieren interconectar. EMIB elimina la limitación del tamaño del DIE y la complejidad en la construcción. Se reduce a un puente de silicio de tamaño reducido que se sitúa en los bordes de los DIE que se quieren interconectar.

Permite que el chip de mayor tamaño se pueda conectar en múltiples dimensiones. Además, permite eliminar las limitaciones físicas adicionales en la construcción de chips heterogéneos dentro de los límites teóricos.

Uso de EMIB en los DIE de los procesadores Intel Sapphire Rapids

Durante la Hoy Chips de hace unas semanas Intel dio nuevos datos al respecto de sus próximos procesadores Sapphire Rapids. Estos procesadores se basan en cuatro DIE interconectados mediante la tecnología EMIB. Aunque dieron algunos datos, todos fueron bastante superficiales, sin entrar en profundidad en los mismos.

Intel revelo que Sapphire Rapids llegaría en dos versiones, una sin memoria HMB y otra con. Destaco también que la versión básica utilizará 10 conexiones EMIB y se agregaran cuatro conexiones EMIB en los procesadores que incluyan memoria HBM (haciendo un total de 14 conexiones EMIB). También se ha destacado que el controlador HBM y el controlador DDR5 están separados.

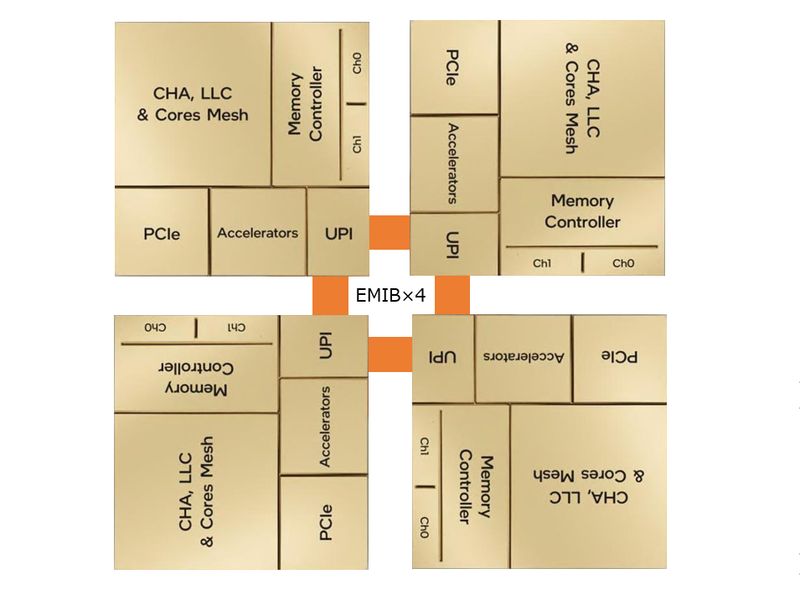

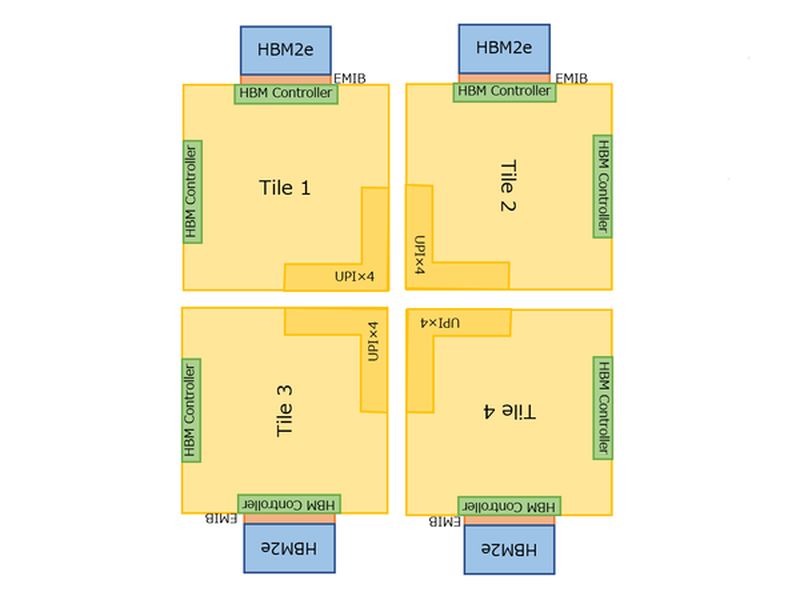

La imagen revelada por Intel muestra una conexión EMIB central que comunica los DIE. Esto hace que el DIE de la esquina superior izquierda se comunique con el que tiene a la derecha y justo debajo, no comunicándose directamente con el DIE opuesto. Dicha configuración hace que tengamos un sistema de 4 conexiones EMIB. Adicionalmente tenemos 4 conexiones EMIB externas, lo cual suma un total de 8 conexiones, entonces, ¿dónde están las que faltan?

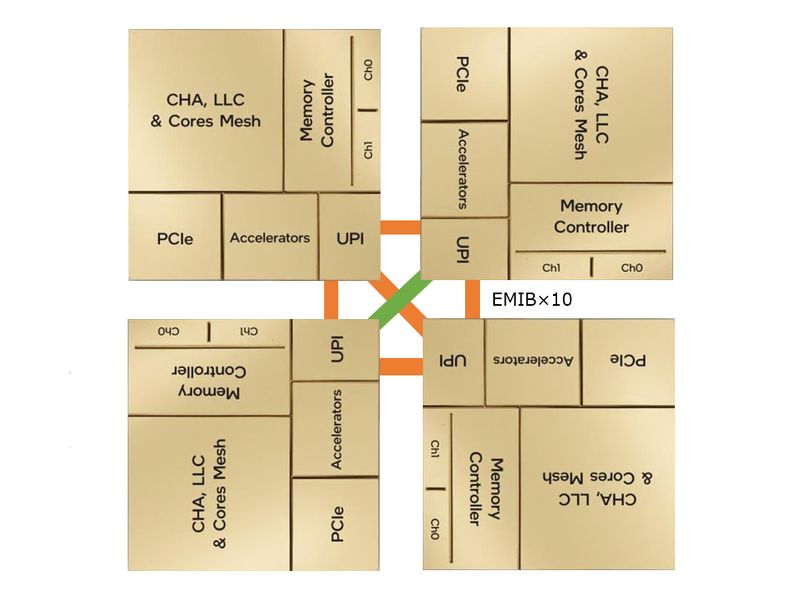

Posible interconexión cruzada

Cada una de las UPI tendría una conexión EMIB externa, lo cual supone que sumen 8 conexiones EMIB. Esto nos deja que nos faltan dos conexiones EMIB por utilizar, si tenemos en cuenta que Intel ha indicado que la versión sin memoria HBM hará uso de 10 conexiones EMIB. Se baraja la posibilidad que existen dos EMIB cruzados que conecten los DIE opuestos que no tendrían conexión. Se puede ver en la siguiente figura esta configuración.

No se han dado datos de esta posible configuración, pero es la más lógica para completar los 10 EMIB disponibles. El cruce en la zona central se puede explicar de manera sencilla. Una de las conexiones EMIB va por el sustrato y la otra conexión va por encima del sustrato. Se habría generado un puente que solventaría la intersección central.

Por ejemplo, el DIE 1 y el DIE 4 están conectados por un EMIB en cuanto a sustrato. Además, el DIE 2 y el DIE 3 se conectan por un EMIB que esta por encima del sustrato. Esto hace que todos los DIE se comuniquen entre sí, evitando que el DIE 1 y DIE 4 se comuniquen pasando la información por el DIE 3 y generando latencia. Aunque esto no está confirmado por Intel.

Configuración memorias HBM en los Intel Sapphire Rapids

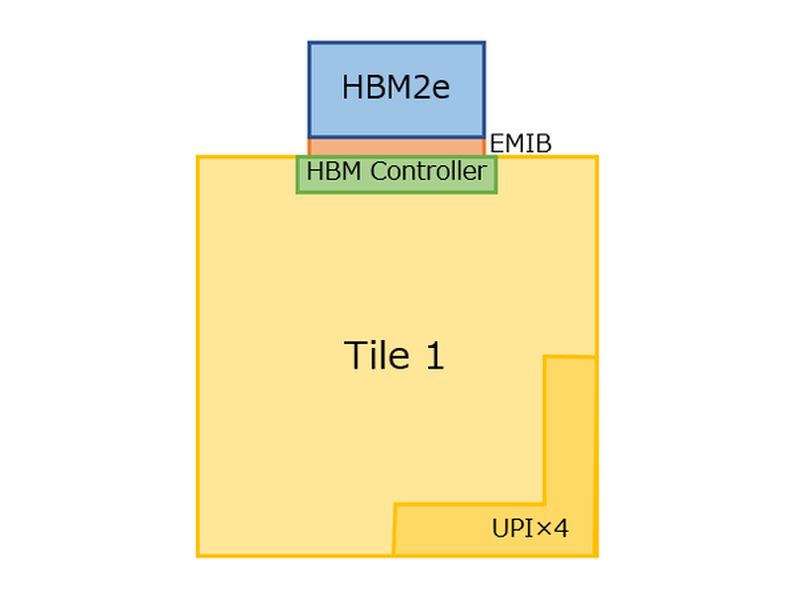

Intel ha destacado que Sapphire Rapids tiene una variante que integra memorias HBM. Estas memorias HBM se sitúan obligatoriamente en la zona externa de los DIE. Destacar que el controlador de las memorias HBM es independiente de la controladora de la memoria DDR5. Las memorias HBM se conectan al DIE mediante una conexión EMIB para ofrecer la mejor comunicación posible.

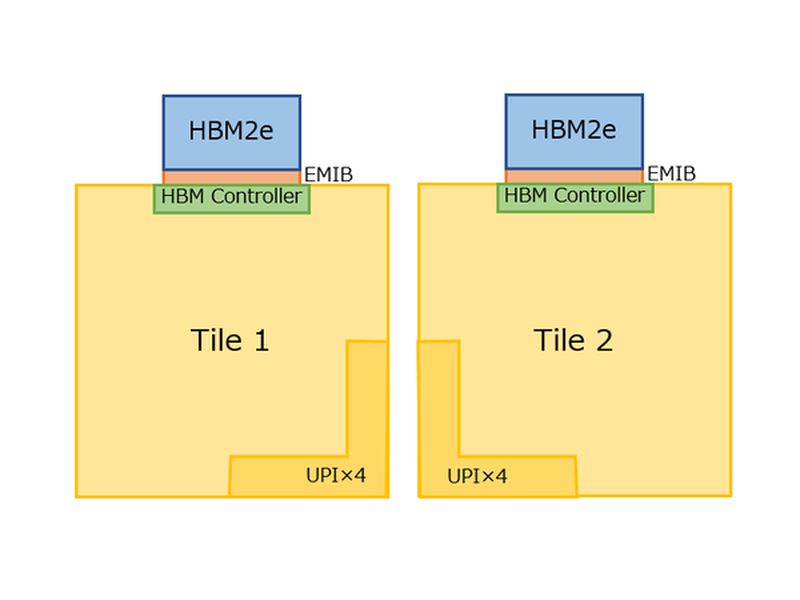

Lo lógico es plantear un solo diseño de DIE con su controladora para memoria HBM. Pongamos que el diseño estándar se basa en el DIE 1, en la esquina superior izquierda. Como vemos en la siguiente imagen.

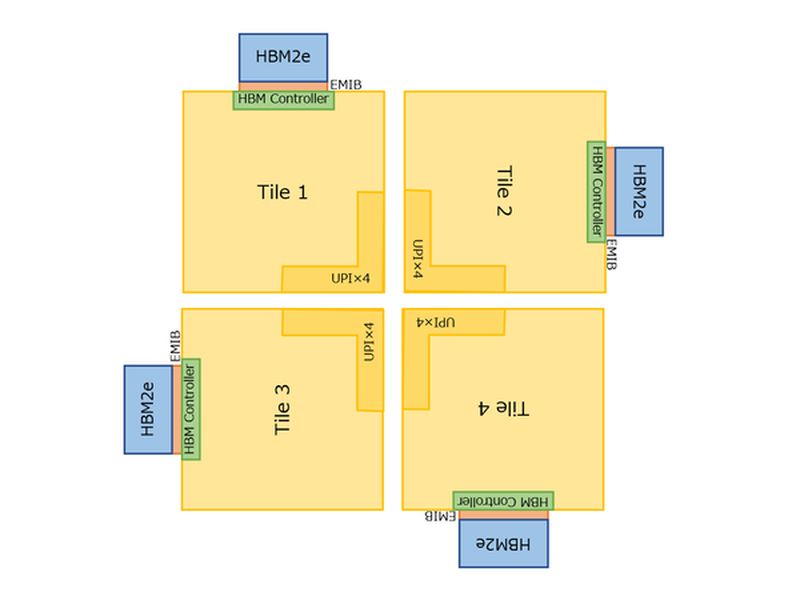

Este diseño único tiene un problema importante y es la rotación. Los UPI deben estar siempre «viéndose», ya que es necesario que estén muy cerca. Esto plantea que cada stack de memoria HBM este en uno de los laterales, como vemos en la siguiente imagen.

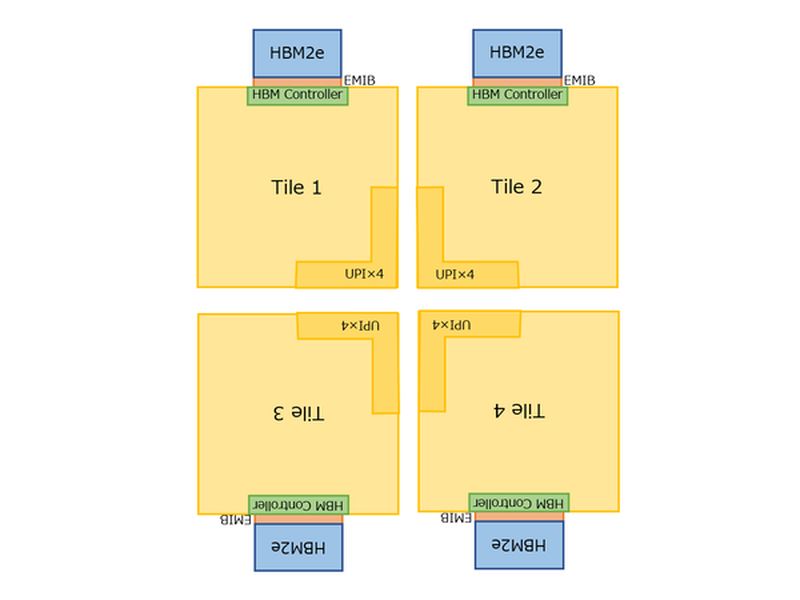

La configuración que vemos sobre estas líneas es inviable. Esta configuración genera un desajuste importante en el tamaño y en la distribución del calor. Así que hay que buscar una solución. Ante la inviabilidad de este diseño, existen dos posibles soluciones que corrijan el problema.

Doble controladora HBM

Una de las posibles soluciones posibles para tener un solo diseño de DIE es que existan dos controladoras HBM. Si tenemos en cuenta que la UPI ocupa los dos laterales interiores, podrían instalarse dos controladoras HBM en los lados exteriores. Esto hace que las rotaciones de los DIE no afecten a la posición de las memorias.

Este diseño presenta un problema importante: hay un gran desperdicio de espacio. Siempre hay una controladora HBM que no se está utilizando y eso implica que hay un elemento que no hace un trabajo. Podemos considerar que este diseño no es útil e implica sacrificar otros elementos o reducir su tamaño.

Dos diseños de DIE

Otra posibilidad es que se dispongan de dos tipos de DIE para evitar integrar dos controladores. Esta solución implica la creación de dos DIE diferentes y requerir dos procesos de fabricación. La creación de dos tipos de DIE implica un aumento en los costes de producción de los procesadores.

Si hablamos de producción, podría implicar que se requieran dos líneas de fabricación de obleas. Cada una se encargaría de realizar, por decirlo de alguna manera, del 50% de los DIE del procesador. Supondría implicar dos líneas solamente en estos procesadores, lo cual implicaría un posible encarecimiento del producto final.

Palabras finales sobre el diseño de los Intel Sapphire Rapids

Como podemos ver, pese a que Intel ha dado datos al respecto de los procesadores Sapphire Rapids, falta mucho por saber. Dentro de este texto abordamos las posibles configuraciones y diseños de estos nuevos procesadores. Será la primera vez que Intel utilice diferentes DIE en un procesador con conexiones EMIB.

Te recomendamos este artículo con los mejores procesadores del mercado

Alguno puede recordar los procesadores Intel Xeon SoMa con 4 DIE pegados. Estos procesadores fueron una tirada exclusiva para un cliente concreto y no se basaban en EMIB, además de carecer de memoria HBM. Hablamos de procesadores, por lo tanto, totalmente diferentes.

Seguramente Intel revele todos los datos de construcción de los Sapphire Rapids durante el lanzamiento. Aunque más allá de su diseño arquitectónico final, lo que más puede interesar es saber el rendimiento. EMIB se posiciona como una gran tecnología de alto rendimiento y eficiencia que puede eliminar el cuello de botella generado por el empaquetado 2.5D.

¿Cuál crees que será el diseño final de los procesadores Intel Sapphire Rapids?