En multitud de noticias, artículos y especialmente review de procesadores AMD aparece el llamado bus Infinity Fabric o IF. En este artículo intentaremos explica de una forma sencilla pero lo más completa posible en qué consiste este bus, qué beneficios tienen para las CPU de AMD y las novedades que se incluyen en procesadores Ryzen 5000.

Uno de los elementos más importantes de un procesador será su bus de datos y de instrucciones. En definitiva, las carretas encargadas de transportar los datos en forma de 0 y 1 entre los distintos elementos que lo componen, núcleos, memoria caché e interfaz de entrada salida. Si quieres conocerlo mejor, ¡empezamos con este artículo!

Índice de contenidos

Bus Infinity Fabric qué es

Infinity Fabric es el nombre que la empresa AMD ha dado a su arquitectura de comunicación e interconexión de sistemas. Dicha arquitectura está patentada por el propio fabricante, así que solamente será de uso exclusivo para los componentes de AMD. Fue presentada a comienzos de 2017, con la implementación de la nueva generación de procesadores AMD Ryzen y su arquitectura Zen.

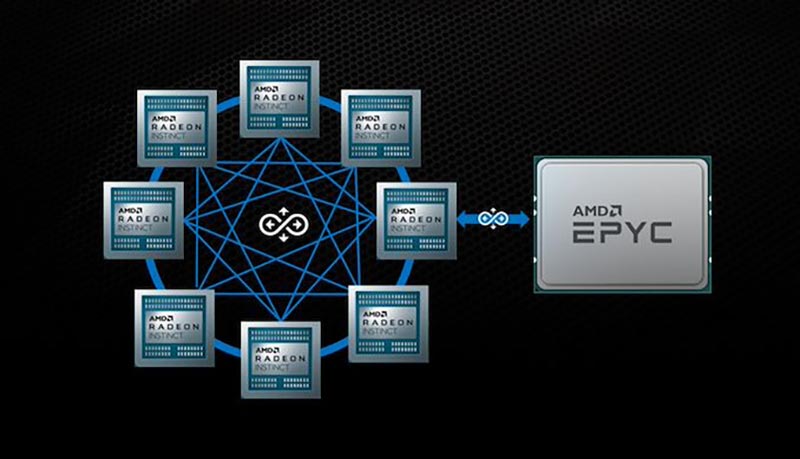

Fue un enorme paso delante de AMD tras años de sequía por las inconsistentes arquitecturas Bulldozer y Excavator, poniendo de nuevo en una posición competitiva a la marca roja. Antes hemos hecho referencia a que Infinity Fabric interconecta sistemas, y es que no solamente está pensado para enlazar los componentes internos de un procesador o un chip gráfico. La idea es llevarlo más lejos, interconectando varios componentes entre ellos como CPU y GPU, o distintas unidades de computación a través de PCIe como ocurre con los procesadores AMD EPYC de servidor.

Funcionamiento de Infinity Fabric en procesadores

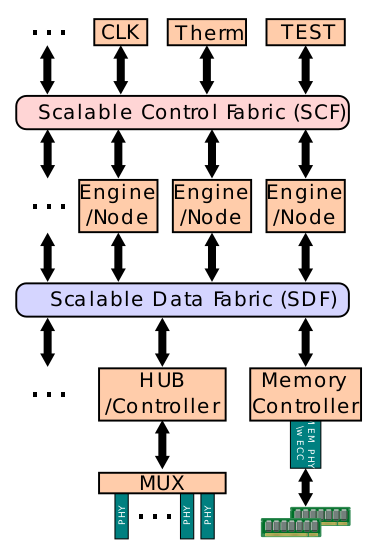

La idea de Infinity Fabric es comunicar los componentes internos de un procesador a nivel de datos y de control, así que para ello utiliza dos niveles o planos de comunicación: SDF o Scalable Data Fabric y SCF o Scalable Control Fabric. El término Scalable hace referencia a que es un bus que en principio se puede extender de forma eficiente a una cantidad de nodos cada vez más grande de forma sencilla.

SDF es el sistema de comunicación evolución de HyperTransport por el que viajan los datos de Infinity Fabric. Este se encarga de transportar los datos desde cada núcleo hacia la memoria caché o el I/O Hub (interfaz de entrada/salida de la CPU). De igual forma, se encarga de interconectar los carriles de memoria RAM, PCIe e incluso USB a la CPU solamente con las restricciones que se marquen en el diseño propio del procesador. Por ello no usa una topología totalmente definida, sino que a veces funciona en bus (caché – núcleo) o en malla (enlaces PCIe).

Gracias a SDF es posible conectar los diferentes núcleos dentro del procesador entre ellos mediante la interfaz Cache-Coheren Master o CCM. A su vez se conecta con un complejo especialmente diseñado para la entrada y salida, el cIOD, el cual actúa como puente norte de nuestro equipo. Desde el cIOD se conectan los carriles PCIe con el IOMS (Interfaz Maestro / Esclavo) y la memoria RAM con el UMC (Controlador de Memoria Unificado).

Del plano de comunicación se encarga el SCF, que de igual forma conectará la Unidad de Gestión del Sistema (SMU) con los demás elementos, como el cIOD, los núcleos y la memoria caché. Este bus se puede extender a varias unidades de procesamiento bajo una misma placa, por ejemplo, para los AMD Threadripper y sus 4 CCD o en procesamiento en paralelo con los AMD EPYC de servidores.

CCD, CCX y caché L3 unificada en Zen 3

Pasamos al caso concreto de funcionamiento de Infinity Fabric en los procesadores AMD Ryzen 5000 y su arquitectura Zen 3. Los núcleos de estas CPU utilizan un proceso de fabricación en 7 nm que mejoran muchos aspectos respecto a la generación anterior Zen 2. Muchos de ellos se escapan a nuestro conocimiento, pero de forma efectiva han conseguido aumentar el IPC (Instrucciones por ciclo) hasta un 19% respecto a la anterior generación.

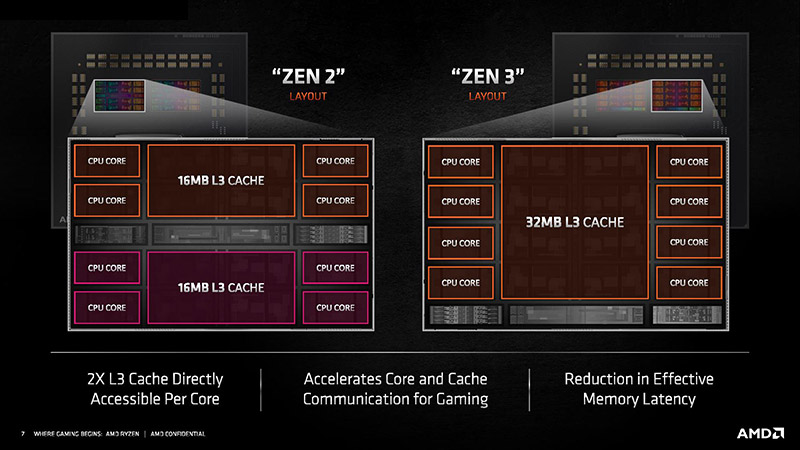

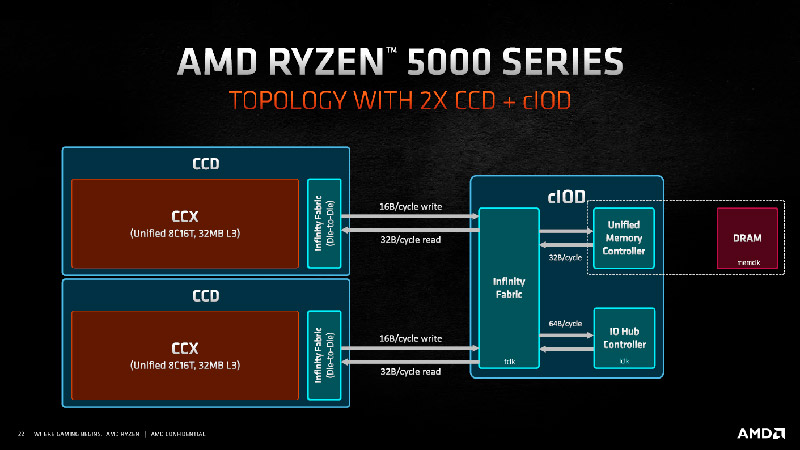

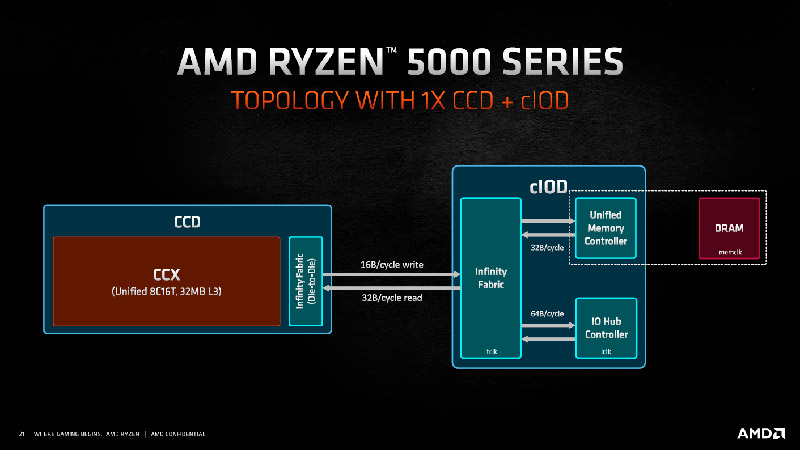

Lo que sí se puede ver de forma clara es la nueva distribución de matrices de procesamiento dentro de un procesador Zen 3 con ayuda de los diagramas facilitados por AMD. Llamaremos CCD (Core Chiplet Die) a cada una de estas matrices que contienen los núcleos y la caché L3, para los amigos, Chiplets a secas. Dentro de los CCD tendremos los CCX (Core Complex), que contienen los núcleos y las cachés L2 y L1.

Pues bien, una de las novedades de Zen 3 radica en la simplificación de los CCD y CCX de las CPU. Mientras que en Zen 2 teníamos dos CCX, cada uno con 4 núcleos y 16 MB de caché L3, Zen 3 unifica todo esto en un único CCX dentro del CCD. Como podemos ver, Infinity Fabric se simplifica bastante, pues ahora el bloque completo de caché L3 está disponible para los 8 núcleos por igual. La velocidad de acceso será mayor al existir menos carriles, mejorando el rendimiento multihilo en programas y juegos.

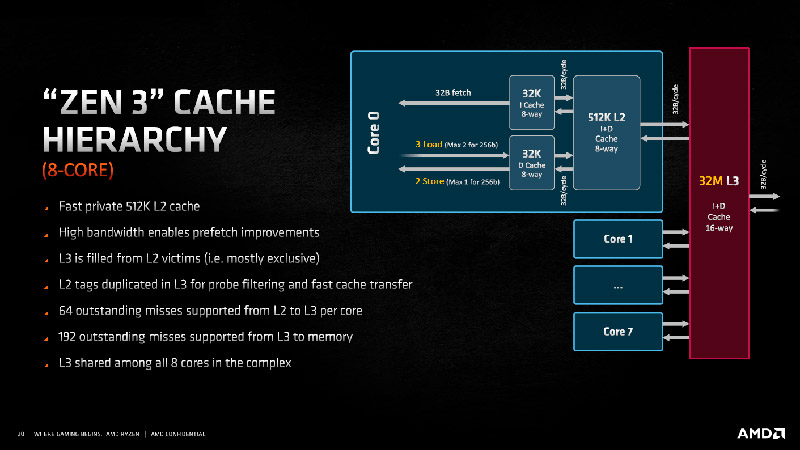

En el interior de cada núcleo, tendremos un bloque de caché L2 de 512 KB exclusivo para él que se comunica con L3 mediante instrucciones de 32 bits/ciclo. Y a su vez encontraremos una caché L1 dividida en bloques de Datos e Instrucciones de 32 KB que a se comunican con L2 mediante 32 bits/ciclo. A partir de aquí se introducen novedades en la CPU añadiendo 1 carga más por ciclo y 32 bits de fetch que mejoran la capacidad.

Pequeña limitación de Infinity Fabric al usar 1 o 2 CCD

Un punto importante que debe quedarnos claro a los usuarios de AMD Ryzen es la gestión de datos entre memoria RAM y procesador. Además, por razones de implementación y arquitectura ha permanecido igual en arquitecturas anteriores, expliquémoslo.

Cuando tenemos un procesador con dos CCD, por ejemplo, el 5900X y 5950X que utilizan núcleos de ambos complejos, la comunicación entre CPU y cIOD se realiza a través de dos canales. El canal de escritura maneja 16 bits por ciclo, mientras que el de lectura opera con 32 bits/ciclo. Esto hace que tengamos la capacidad completa en la comunicación RAM – CPU, pues a su vez el UMC se comunica con Infinity Fabric mediante 32 bits/ciclo.

Pero en procesadores como el Ryzen 7 5800X o los anteriores 3700X y 3800X que solamente tienen un CCD el escenario cambia. En este caso el canal de escritura de la RAM estará limitado a 16 bits/ciclo mientras que el de lectura permanece en 32 bits/ciclo. Es por este motivo que experimentamos tasas de escritura en RAM a la mitad de la capacidad de lectura, siendo un ligero inconveniente en el rendimiento. De todas formas, no es un factor demasiado limitante en la práctica.

Mejor aprovechamiento de memorias RAM a altas frecuencias

Otro tema importante sobre el funcionamiento de la memoria RAM serán las frecuencias de los elementos del cIOD e Infinity Fabric. Es otro elemento que AMD ha mejorado para trabajar mejor con memorias de altas frecuencias.

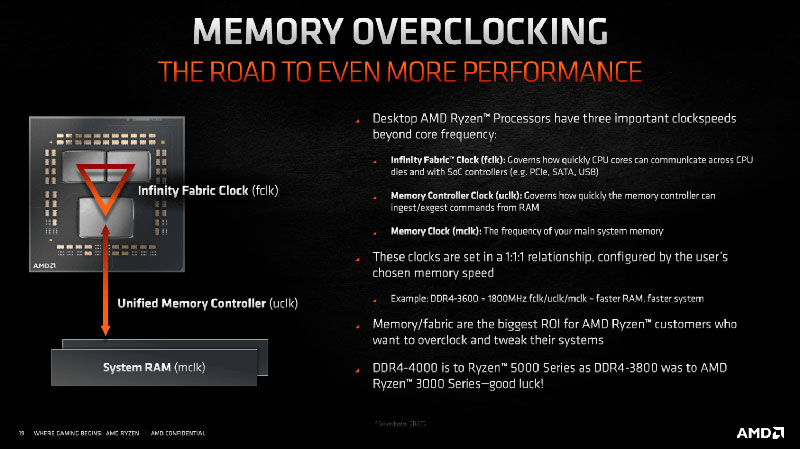

La configuración interna se mantiene igual como ya hemos visto en el apartado anterior, así que el secreto serán sus frecuencias de trabajo. Ahora Infinity Fabric Clock (fclk), Memory Controller Clock (uclk) y Memory Clock (mclk) van a trabajar en una relación 1:1:1 cuando el usuario configure la frecuencia de memoria activando el perfil de overclocking.

Esto también era posible en Zen 2, pero en Zen 3 se aumenta la capacidad hasta los 2000 MHz frente a los 1800 MHz anteriores. Esto significa que ahora se soportan memorias DDR4 de hasta 4000 MHz efectivos sin afectar a la estabilidad, ya que cuando se pasa de esa frecuencia, el reloj uclk pasa a usar un multiplicador bajando su frecuencia a la mitad.

Ha existido confusión en la comunidad acerca de la compatibilidad de memorias con AMD Ryzen Zen 3, afirmando que solo rendiría al máximo con memorias de 4000 MHz. Esto es completamente falto, el sistema rendirá perfectamente con cualquier tipo de memoria desde los 2400 hasta los 4000 MHz. Si bien a partir de ahí, al activarse el multiplicador, no se extraerá el máximo rendimiento de memorias de 4400 MHz o 5000 MHz, por ejemplo. No obstante, estas frecuencias también son compatibles, pues las placas base X570 y B550 soportan memorias de muy alta frecuencia actualmente.

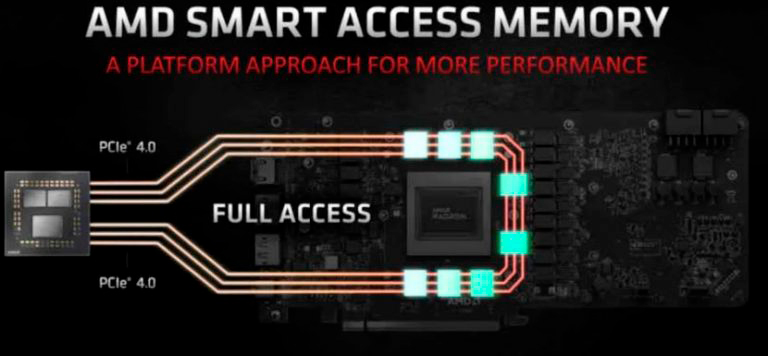

Nueva función Smart Access Memory

Infinity Fabric es el umbral de la nueva tecnología Smart Access Memory implementada por AMD en la arquitectura de tarjetas gráficas RDNA 2 y procesadores Zen 3. SAM es capaz de ampliar el canal de datos desde el procesador hasta las nuevas gráficas Radeon RX 6000 para compartir su memoria VRAM a través de los carriles PCIe 4.0. De esta forma es posible aprovechar la potencia de la memoria GDDR6 por el procesador para mejorar la comunicación entre componentes.

De esta forma el intercambio de información entre ambos chips utilizará la capacidad de los 16 carriles PCI que aún no es explotada en las tarjetas actuales. Al menos parte de ella, así se puede eliminar gran parte del cuello de botella existente entre estos dos elementos y el resto del sistema.

Esta característica por ahora estará disponible en placas con chipsets AMD B550 y X570 siempre que tengan la actualización AMD AGESA 1.1.0.0 o superior instalada, así como el controlador AMD Radeon Software 20.11.2 o posterior. Funcionará con las CPU Ryzen 5000 y las GPU Radeon RX 6000. Una buena noticia es que placas con chipsets anteriores como X470 o B450 también serán compatibles con una actualización de BIOS

La alternativa que tenemos en Nvidia será la función Resizable BAR, de la que hablamos en otro artículo que dejaremos al final.

El nombre de Infinity también se ha expandido a las tarjetas gráficas, pues en las GPU de nueva generación se implementa un nuevo nivel de memoria caché Infinity Cache. Su función es la de mejorar la comunicación entra GDDR6 y GPU a través de un bloque de memoria caché ultrarrápido de gran capacidad con sus 128 MB. La configuración consistirá en 16 canales de 64 bits trabajando a 1,94 GHz, capaces de generar un bus de 1024 bits para cuadruplicar los 256 bits de ancho de bus que tiene la memoria GDDR6. Por su parte la memoria VRAM trabajará a un ancho de banda de 512 GB/s y velocidad de 16 Gbps.

Conclusiones acerca de Infinity Fabric

Estas son las principales claves que un usuario de AMD debería conocer sobre su plataforma. Infinity Fabric ha traído muchas alegrías al “Team Red” ya desde los primeros procesadores ZEN. La revolucionaria arquitectura basada en chiplets es sin duda el camino a seguir para obtener procesadores escalables en núcleos, caché y más unidades funcionales.

Gracias a este bus resulta sencillo entender la comunicación interna de elementos funciones de un procesador y como actúa con memoria y carriles PCIe. Además, es muy sencillo activar y desactivar núcleos en los modelos de procesador, permitiendo además al usuario overclockear dicho bus para incrementar el rendimiento.

Su eterno rival Intel por ahora no está utilizando chipsets en sus procesadores de portátiles y escritorio, si bien podemos encontrar en dados diferentes los gráficos integrados y el procesador en sí mismo. Veremos cómo se presentan en el futuro próximo los procesadores Alder Lake de 10 nm para escritorio, en los que se prevé un incremento sustancial de núcleos.

Os dejamos con más tutoriales interesantes relacionados con el tema: