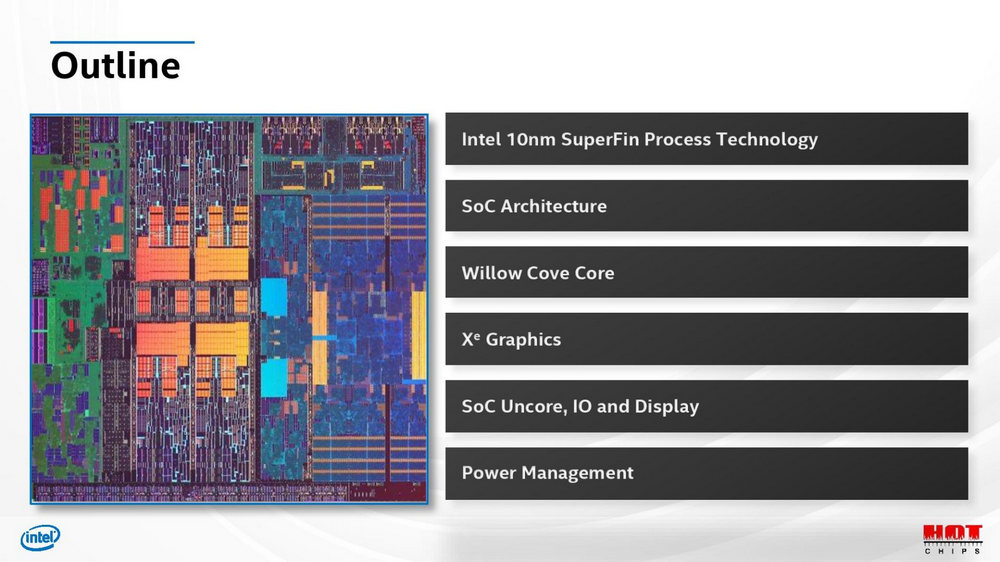

Intel compartió más detalles sobre Tiger Lake bastante detallado, que incluye capturas del die con un chip de cuatro núcleos. Los procesadores Tiger Lake marcan el debut de los transistores SuperFin de 10nm de Intel. Intel factura estos transistores optimizados, que son una iteración de los 10nm existentes, como la mejora del rendimiento que se espera normalmente de un nuevo nodo.

Intel Tiger Lake, mas detalles y primeras capturas del die

Entre los aspectos más destacados se incluyen mejoras de rendimiento de aproximadamente un 15-20% con los mismos voltajes/ relojes en algunas áreas, y velocidades pico de reloj mucho más altas, probablemente en el rango de 5GHz para las piezas de portátiles.

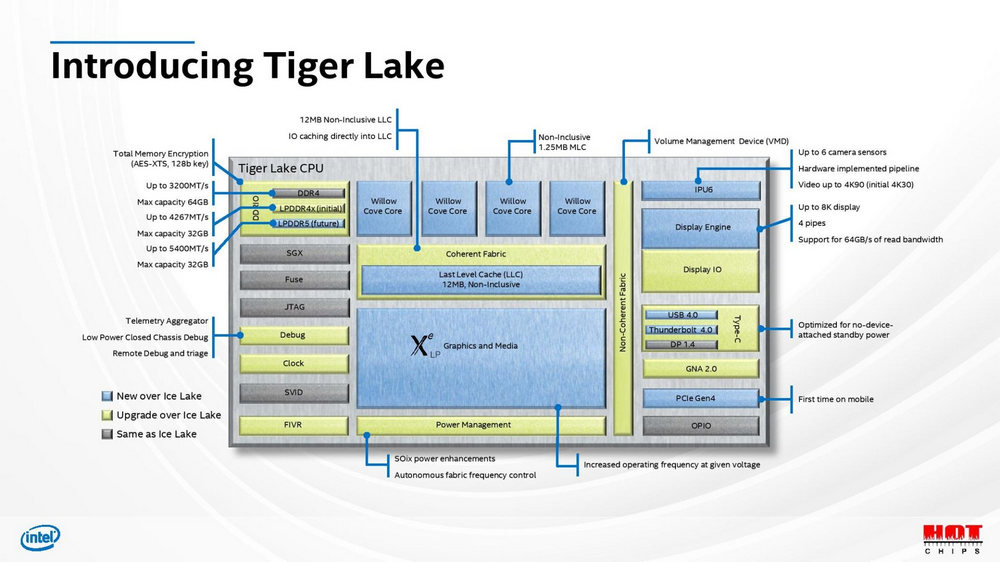

Intel combina esos transistores optimizados con nuevos núcleos Willow Cove, mayores capacidades de caché, ajuste para alta velocidad, gráficos Xe LP de Intel (que ofrecen hasta el doble de rendimiento que los iGPU de Intel de generaciones anteriores) y compatibilidad con hasta la memoria LPPDR5-5400 y PCIe 4.0.

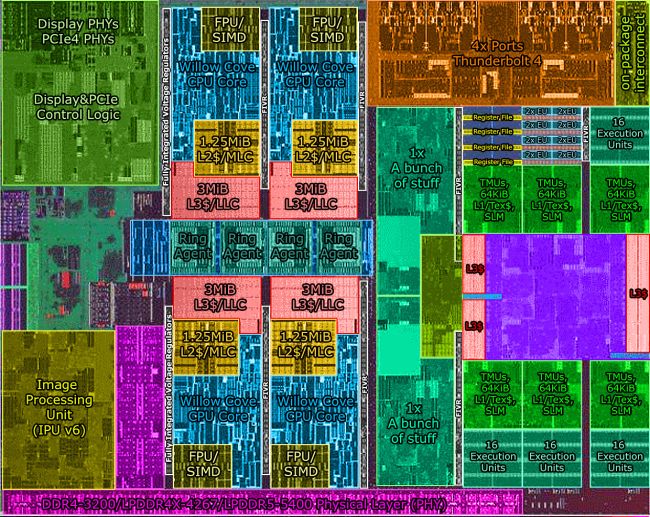

Aquí podemos ver la imagen del die que Intel compartió durante su presentación en Hot Chips 2020. La gran zona azul de la esquina inferior derecha es probablemente la unidad gráfica Xe LP (que comprende aproximadamente el 33% del dado).

Intel anuncia una nueva capacidad de caché aumentada para su L2 (MLC) y L3 (LLC), que ahora pesan 1,25 MB y 12 MB, respectivamente. Intel aumentó la capacidad de L2 esta vez, lo que habría resultado en un insostenible 5MB de datos copiados para ser mantenidos en la caché L3. Por lo tanto, la empresa pasó a un esquema no inclusivo que no requiere una copia de los datos L2 en la caché L3, lo que deja espacio para conjuntos de trabajo más grandes en la caché L3 compartida.

También vemos el soporte para la memoria LPPDRx-4267 en los primeros modelos de Tiger Lake, y ese incremento en el rendimiento ayudará a alimentar el motor de gráficos Xe LP.

Intel también pasó a la microarquitectura de bus de anillo dual, aunque esto varía significativamente de los buses de anillo dual más antiguos que se encuentran en las matrices de Skylake-X de antaño. 172GB/s es el ancho de banda en el die.

Intel también puso hincapié en el uso del escalado dinámico de voltaje/frecuencia (DVFS), que ahora es controlador por el hardware y no por el sistema operativo, mejorando la latencia y así el consumo de energía más eficientemente.

Pueden ver mas detalles en Toms Hardware.