El ingeniero retirado de VLSI y analista de la industria, @chiakokhua, ha teorizado sobre cómo podría ser «Rocket Lake-S», que se remonta a noviembre de 2019, y que ahora está resurgiendo en las comunidades tecnológicas. Aparentemente, Intel está diseñando estos procesadores para ser módulos multichip, similares a «Matisse» en algunos aspectos, pero diferentes en otros.

Rocket Lake-S podría contener módulos multichip similar a AMD Matisse

英雄所見略同?要錯,一起錯吧。🙃 pic.twitter.com/yHPDLkz0N9

— RetiredEngineer® (@chiakokhua) June 11, 2020

@chiakokhua estuvo entre las primeras voces que hablaron de los procesadores AM4 con sockets Ryzen de tercera generación como módulos multichip construidos en diferentes procesos de fabricación de silicio, lo cual era una teoría increíble en ese momento, pero acertó.

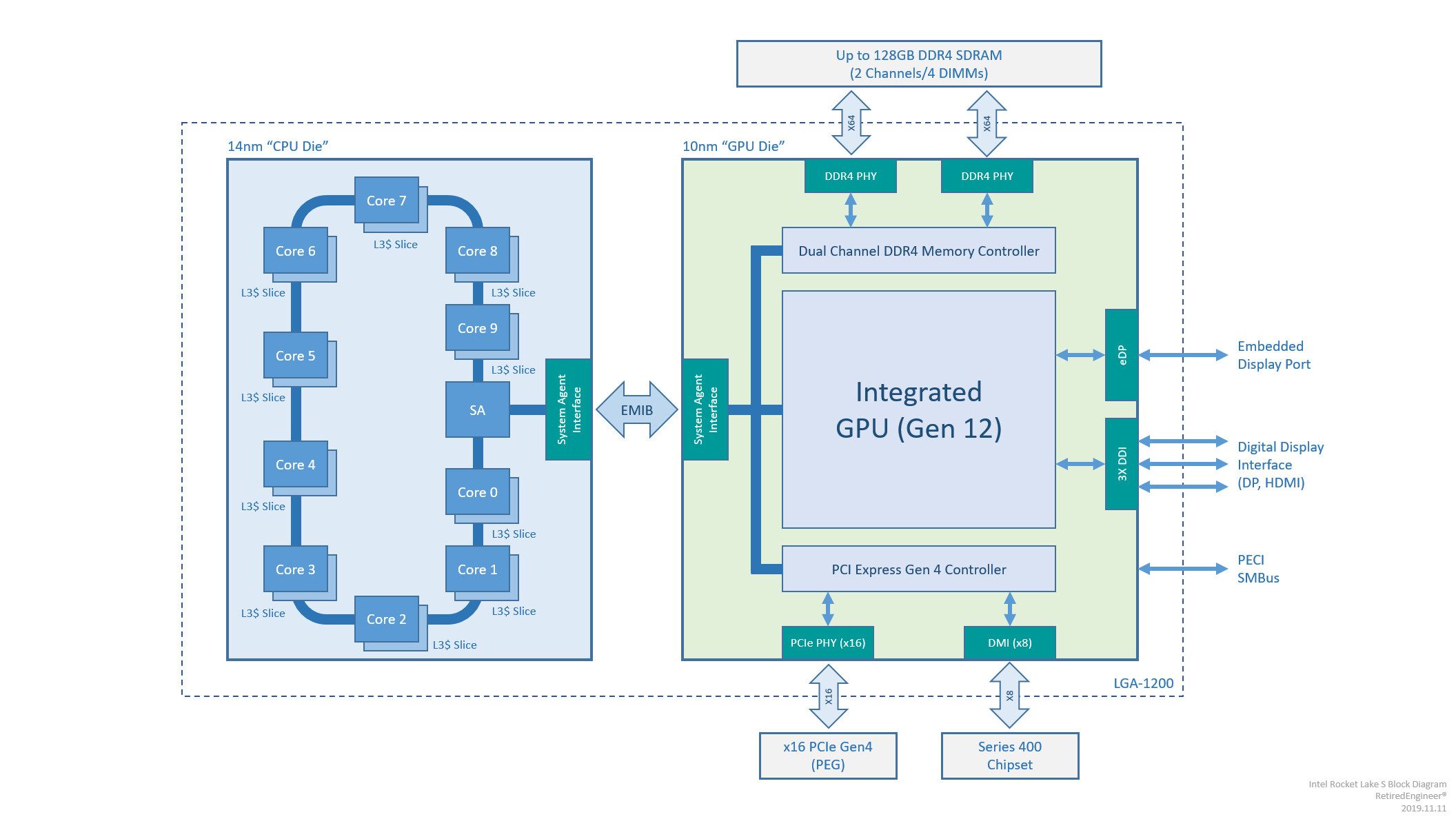

Aparentemente, «Rocket Lake-S» es un módulo multichip con un nodo de 14 nm que contiene los núcleos de la CPU; y un nodo de 10 nm que contiene los componentes sin núcleo. AMD «Matisse» y «Vermeer» también tienen esa división de trabajo, pero los núcleos de la CPU están situados en matrices con un proceso de fabricación de silicio más avanzado (7 nm), que la matriz con los componentes sin núcleo (12 nm).

Visita nuestra guía sobre los mejores procesadores del mercado

El nodo de CPU de 14 nm en «Rocket Lake-S» contiene núcleos de CPU «Willow Cove» que supuestamente introducen importantes ganancias de IPC sobre «Skylake».

El nodo de la GPU de 10 nm (alias «uncore die») incluye la GPU Gen12 Xe del procesador con hasta 96 unidades de ejecución, un controlador de memoria DDR4 de doble canal y PCI-Express 4.0, además de otros componentes menores relacionados con la iGPU, como sus motores de visualización y multimedia.

El supuesto MCM de «Rocket Lake-S» ofrece un total de 24 líneas de PCI-Express. 16 de ellas están asignadas como PEG (PCI-Express Graphics, o la ranura principal PCI-Express x16 de la plataforma); y 8 carriles están asignados como bus de chipset. En microarquitecturas pasadas, incluyendo «Comet Lake-S», el procesador sólo sacaba 20 carriles, 16 de los cuales son hacia el PEG, y 4 hacia el chipset-bus (DMI).

[irp]Esta no es información oficial, así que tomadlo como tal, incluso el diagrama que ha compartido este ingeniero. Sin embargo, es una información a tener en cuenta. Os mantendremos informados.