La caché es una parte muy importante de los procesadores modernos, y un cambio importante en esta parte del chip suele significar que se vienen grandes mejoras en el procesador en general. SANDRA apunta a fuertes modificaciones en la caché L3 de Zen 2.

SANDRA apunta a 32 MB de caché L3 por cada chiplet Zen 2 de 8 núcleos

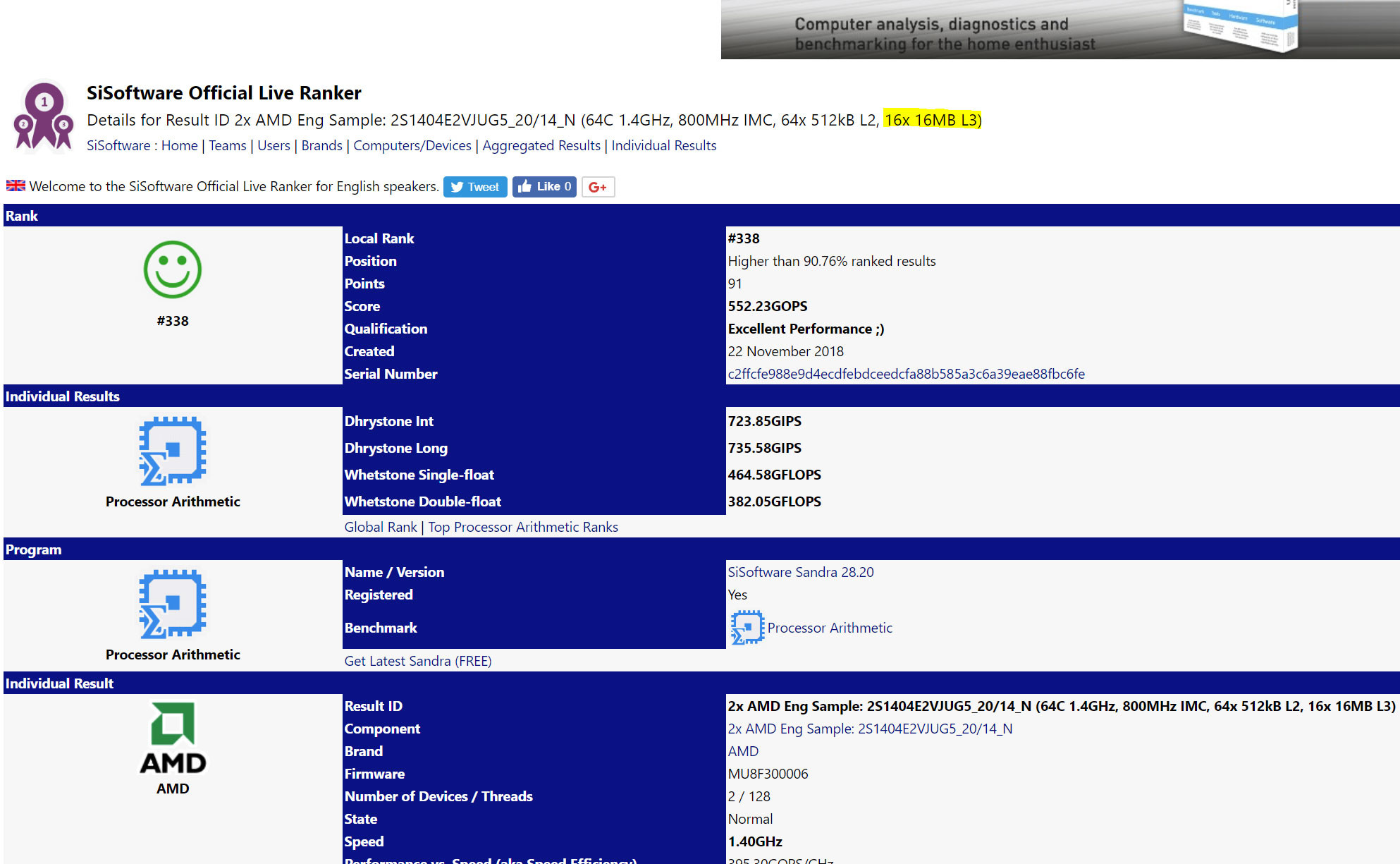

Una entrada de la base de datos de SANDRA de SiSoft muestra datos sobre un procesador AMD EPYC AMD y arroja luz sobre la jerarquía de caché de este modelo. Cada procesador EPYC Rome de 64 núcleos se compone de ocho chiplets de ocho núcleos Zen 2 fabricados a 7 nm, que convergen en un controlador de E / S fabricado a 14 nm. Este controlador se encarga de manejar la memoria y la conectividad PCIe del procesador. El resultado menciona la jerarquía de caché, con 512 KB de caché L2 dedicada por núcleo y «16 x 16 MB de caché L3». Para el Ryzen 7 2700X, SANDRA lee la caché de L3 como «2 x 8 MB L3», correspondiente a la cantidad de 8 MB L3 por CCX.

Te recomendamos la lectura de nuestro artículo sobre Rendimiento de AMD EPYC Rome frente a Intel Cascade Lake en 2S

Con SANDRA detectando «16 x 16 MB L3» para Rome de 64 núcleos, es muy probable que cada uno de los chiplets de 8 núcleos tenga dos partes de caché de 16 MB L3, y que sus 8 núcleos se dividan en dos CCX de cuatro núcleos con 16 MB de caché L3, cada una.Esta duplicación en la memoria caché L3 por CCX podría ayudar a los procesadores a optimizar las transferencias de datos entre el chiplet y la E/S para rendir mejor. Esto es particularmente importante ya que el troquel de E/S controla la memoria con su controlador monolítico de memoria DDR4 de 8 canales.

[irp]AMD ha hecho profundos cambios a nivel arquitectónico con Zen 2, habrá que esperar hasta que salgan a la venta para ver en que se traducen realmente todas estas mejoras, pero por ahora pinta bastante bien.