Qué son los LANES del procesador y la importancia en Multi-GPU

En este artículo os explicaremos que son los LANES del procesador. Pero antes tenemos que conocer que son los PCI Express (Peripheral Component Interconnect Express), abreviado oficialmente como PCIe o PCI-e, es un estándar de bus de expansión de computadora de alta velocidad, diseñado para reemplazar los estándares de bus más antiguos como PCI, PCI-X y AGP.

Índice de contenidos

Qué es la interfaz PCI Express y cómo funciona

PCIe tiene numerosas mejoras con respecto a los estándares más antiguos, que incluyen un mayor rendimiento máximo del bus del sistema, un menor conteo de pines de E / S y una huella física más pequeña, mejor escalamiento del rendimiento para los dispositivos del bus, un mecanismo más detallado de detección e informe de errores (Advanced Error Reporting, AER, y la funcionalidad nativa de intercambio en caliente. Además, las revisiones más recientes del estándar PCIe brindan soporte de hardware para la virtualización de E/S.

Te recomendamos la lectura de nuestro artículo sobre Mejores procesadores del mercado

Definida por su número de lanes, la interfaz eléctrica PCI Express también se usa en una variedad de otros estándares, especialmente la interfaz de la tarjeta de expansión para PC portátil ExpressCard y las interfaces de almacenamiento SATA Express y M.2. Las especificaciones de formato son mantenidas y desarrolladas por el PCI-SIG (PCI Special Interest Group), un grupo de más de 900 compañías que también mantienen las especificaciones convencionales de PCI. PCIe 3.0 es el último estándar para tarjetas de expansión, que está en producción y disponible en PCs personales convencionales.

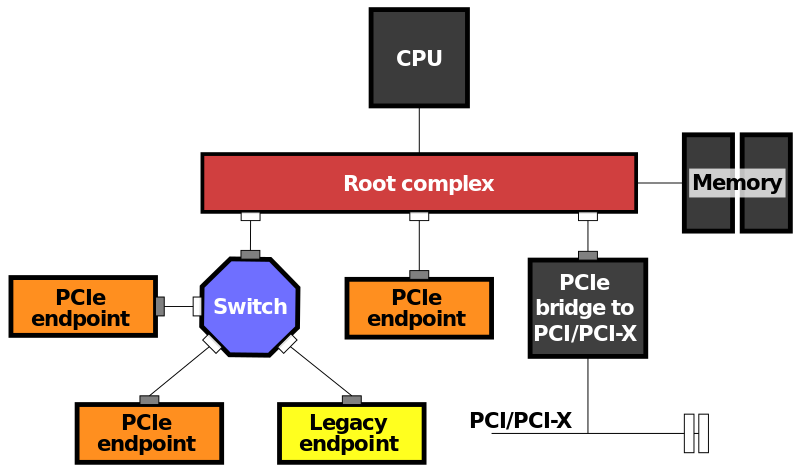

Topología punto a punto

Conceptualmente, el bus PCI Express es un reemplazo en serie de alta velocidad del bus PCI / PCI-X anterior. Una de las diferencias clave entre el bus PCI Express y el PCI anterior es la topología del bus; PCI utiliza una arquitectura de bus paralelo compartida, en la que el host PCI y todos los dispositivos comparten un conjunto común de direcciones, datos y líneas de control. En contraste, PCI Express se basa en una topología punto a punto, con enlaces seriales separados que conectan cada dispositivo al complejo raíz. Debido a su topología de bus compartido, el acceso al bus PCI más antiguo está arbitrado y se limita a un maestro a la vez, en una sola dirección. Además, el esquema de reloj PCI más antiguo limita el reloj del bus al periférico más lento del bus. Por el contrario, un enlace de bus PCI Express admite la comunicación full-duplex entre dos puntos finales, sin limitación inherente en el acceso simultáneo a través de múltiples puntos finales.

En términos de protocolo de bus, la comunicación PCI Express está encapsulada en paquetes. El trabajo de empaquetado y desempaquetado de datos y el tráfico de mensajes de estado es manejado por la capa de transacción del puerto PCI Express. Las diferencias radicales en la señalización eléctrica y el protocolo de bus requieren el uso de un factor de forma mecánico diferente y conectores de expansión. Las ranuras PCI y las ranuras PCI Express no son intercambiables. A nivel de software, PCI Express conserva la compatibilidad con versiones anteriores de PCI.

Qué son los LANES PCI Express del procesador

El enlace PCI Express entre dos dispositivos puede constar de uno a 32 lanes. En un enlace de varios lanes, los datos del paquete se dividen en líneas y el rendimiento máximo de datos se escala con el ancho del enlace general. El recuento de lanes se negocia automáticamente durante la inicialización del dispositivo, y puede ser restringido por cualquiera de los puntos finales. Por ejemplo, una tarjeta PCI Express de un solo lane (× 1) se puede insertar en una ranura de varios lanes (× 4, × 8, etc.), y el ciclo de inicialización negocia automáticamente el mayor recuento de lanes con soporte mutuo. El enlace puede configurarse dinámicamente para usar menos lanes, proporcionando una tolerancia a fallos en caso de que haya lanes defectuosos o poco confiables. El estándar PCI Express define ranuras y conectores para múltiples anchos: × 1, × 4, × 8, × 12, × 16 y × 32. Esto permite que el bus PCI Express sirva para ambas aplicaciones sensibles al coste donde no se necesita un alto rendimiento, así como aplicaciones de rendimiento crítico como gráficos 3D, redes y almacenamiento empresarial.

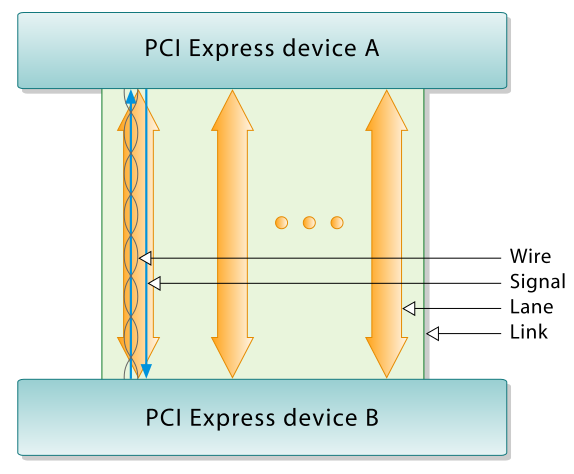

Un lane se compone de dos pares de señalización diferencial, con un par para recibir datos y el otro para transmitir. Por lo tanto, cada lane está compuesto por cuatro cables o trazas de señal. Conceptualmente, cada lane se usa como un flujo de bytes de dúplex completo, que transporta paquetes de datos en formato de «byte» de ocho bits simultáneamente en ambas direcciones entre los puntos finales de un enlace. Los enlaces físicos de PCI Express pueden contener de uno a 32 lanes, más precisamente 1, 2, 4, 8, 12, 16 o 32 lanes. Los conteos de lanes se escriben con un prefijo «×» ( por ejemplo, «× 8» representa una tarjeta o ranura de ocho lanes), siendo × 16 el tamaño más grande de uso común. Los tamaños de los lanes también se mencionan a través de los términos «ancho» o «por», por ejemplo, una ranura de ocho carriles podría denominarse «por 8» o como «8 lanes de ancho».

Los lanes PCIe se utilizan en algunos lugares dentro de tu PC. Tu CPU tiene un cierto número de ellos, al menos 16, conectados entre él y al menos una ranura 16x en la placa base. Normalmente estos lanes se usan para tarjetas gráficas, ya sea con una tarjeta que usa todo el canal o con varias tarjetas, cada una con parte del canal. Algunas CPU tienen más lanes de tarjetas gráficas, algunas de las CPU de la serie X de Intel tienen hasta 40 o más.

Algunos lanes conectan su CPU al Platform Controller Hub (PCH). Intel llama a estos lanes DMI, pero en realidad son lo mismo que PCIe. Desde el PCH, los lanes PCIe van a su controlador SATA, a su ranura M.2 compatible con NVMe, a los controladores USB y a varias ranuras PCIe en la placa base para cosas como adaptadores de red, tarjetas de sintonizador de TV y otras. El PCH sirve como multiplexor y, en última instancia, todos estos dispositivos tienen que compartir los lanes DMI disponibles cuando se comunican con la CPU o la memoria principal.

Te recomendamos la lectura de nuestro post sobre los mejores procesadores del mercado

Con esto finaliza nuestro artículo sobre los LANES del procesador y para que sirven. Esperemos que os haya resultado de utilidad.