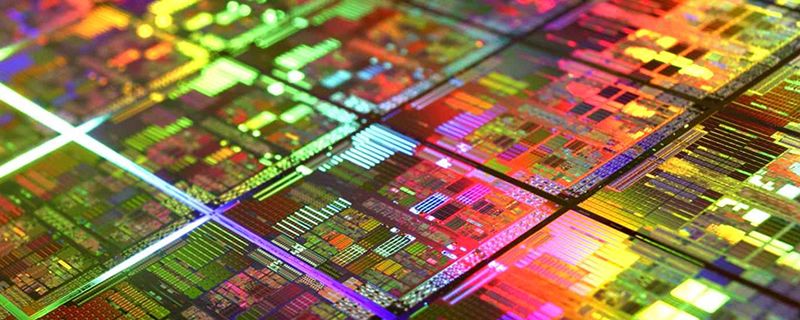

Mientras que los problemas de 10 nm de Intel continúan, TSMC ha seguido avanzando hacia nodos más pequeños, confirmando sus planes de iniciar la ‘producción de riesgo’ del nodo de 5 nm en la segunda mitad de 2019.

TSMC comenzara la producción de riesgo del nuevo nodo en 5 nm el año próximo

Además, TSMC espera que su nuevo nodo de 7 nm represente el 20% de sus ingresos totales durante el año próximo, mostrando la enorme demanda de un nodo de proceso de vanguardia, con TSMC siendo líder en la fabricación de nodos de 7 nm, luego de que GlobalFoundries abandonara la producción de los mismos.

TSMC está planeando desarrollar un nodo FinFET ‘Plus’ de 7 nm, que adopte la tecnología EUV para varias capas en el proceso de fabricación, mientras que FinFET de 5 nm utiliza aún más la tecnología para capas más críticas, reduciendo la necesidad de patrones múltiples. La tecnología EUV llegaría un tiempo luego de que la producción en masa de los 7 nm comience.

Estiman una reducción de área de 45% en comparación con los 7nm

Este cambio también permitirá que los 5 nm ofrezca una cantidad significativa de ‘escalamiento’ de transistores en comparación con los 7 nm, con informes iniciales que estiman una reducción de área de 45% en comparación con los 7nm FinFET, lo que es una mejora bastante importante.

[irp]

En cuanto al contexto, el nodo FinFET de 7 nm de TSMC ya ofrece una reducción de área del 70% sobre el nodo FinFET de 16nm, lo que convierte a el nodo de 5 nm en algo extremadamente compacto, aunque se espera que el ahorro de energía y los aumentos de rendimiento que proporciona los 5 nm sean menores con respecto a los 7 nm.